User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

gx_04.fm.(1.2)

March 27, 2006

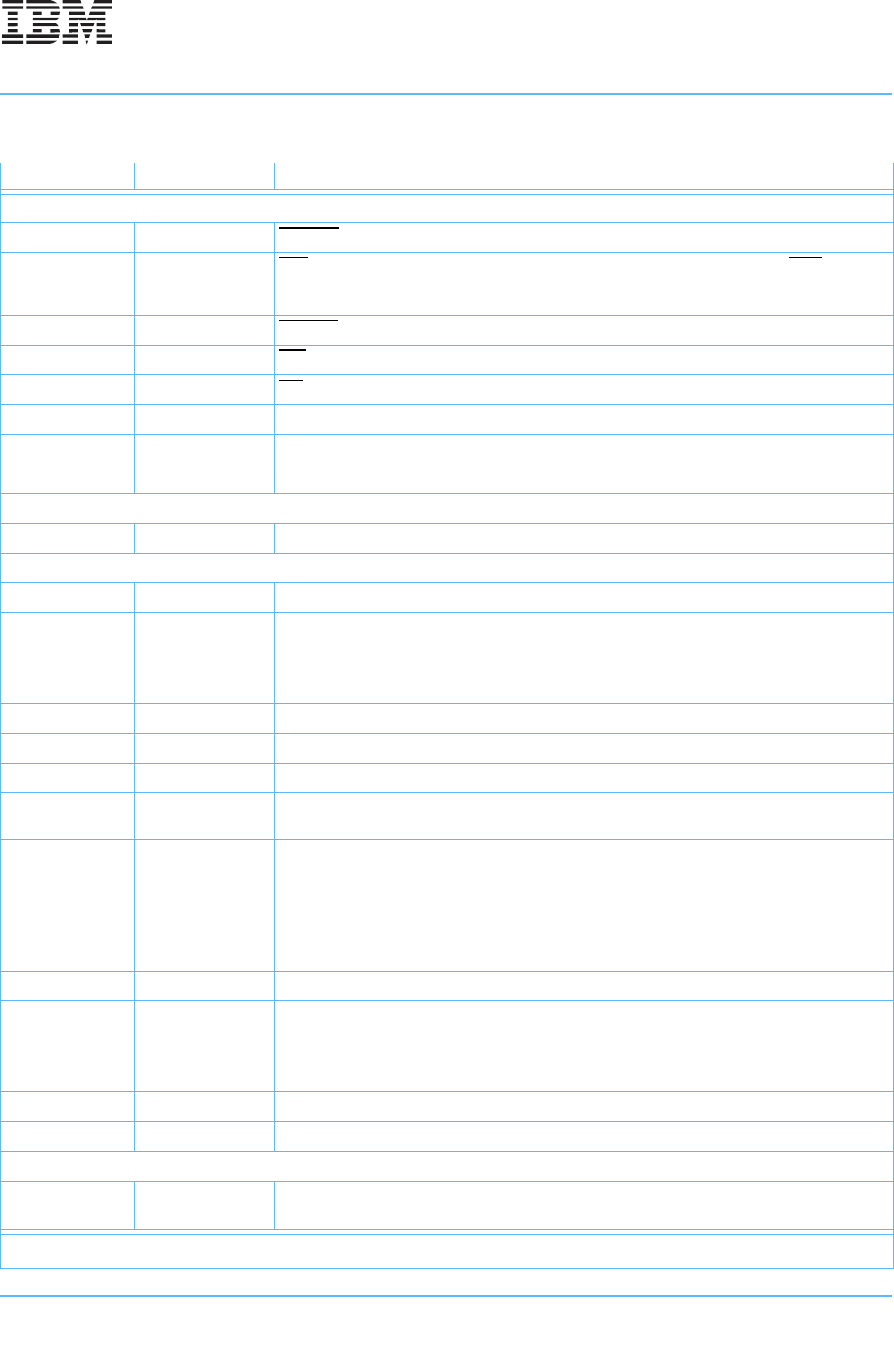

Exceptions

Page 155 of 377

Table 4-3. Exception Priorities

Priority Exception Cause

Asynchronous Exceptions (Interrupts)

0 System Reset HRESET

, POR

1 Machine Check

TEA

, 60x address-parity error, 60x data-parity error, L2 ECC double-bit error, MCP, L2-tag

parity error, data-tag parity error, instruction-tag parity error, instruction-cache parity error,

data-cache parity error, or locked L2 snoop hit

1

2 System Reset SRESET

3SMISMI (system management exception)

4EIINT

(External Exception)

5 PFM Performance-monitor exception

6 DEC Decrementer exception

7 TMI Thermal-management exception

Instruction Fetch Exceptions

0 ISI Instruction storage exception

Instruction Dispatch/Execution Exceptions

0 IABR Instruction address breakpoint exception

1PI

Program exception due to:

1. Illegal instruction

2. Privileged instruction

3. Trap

2SCSystem call

3 FPA Floating-point unavailable exception

4 PI Program exception due to floating-point enabled exception

5DSI

Data-storage exception due to eciwx, ecowx with the enable bit of the External Access Reg-

ister cleared (EAR[E] = 0) (bit 11 of DSISR)

6 Alignment

Alignment exception due to:

• Floating point not word aligned

• lmw, stmw, lwarx, or stwcx not word-aligned

• Either eciwx or ecowx not word-aligned

• Multiple or string access with the little-endian bit set.

• dcbz to write-through or cache-inhibited page or cache is disabled.

7 DSI Data-storage exception due to a block-address-translation (BAT) page-protection violation

8DSI

Data-storage exception due to:

• Any access except cache operations to a segment where SR[T] = 1

• An access that crosses from an SR[T] = 0 segment to an SR[T} = 1 segment

These exceptions are indicated by DSISR[5] = 1.

9 DSI Data-storage exception due to a translation lookaside buffer (TLB) page-protection violation

10 DSI Data-storage exception due to a Data Address Breakpoint Register (DABR) address match

Post Instruction Execution Exceptions

11 Trace

Trace exception due to:

MSR[SE] = 1 or (MSR[BE] = 1 for branches

1. Even though DSISR(5) and DSISR(11) are set by different priority exceptions, both bits can be set at the same time.