User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction-Cache and Data-Cache Operation

Page 148 of 377

gx_03.fm.(1.2)

March 27, 2006

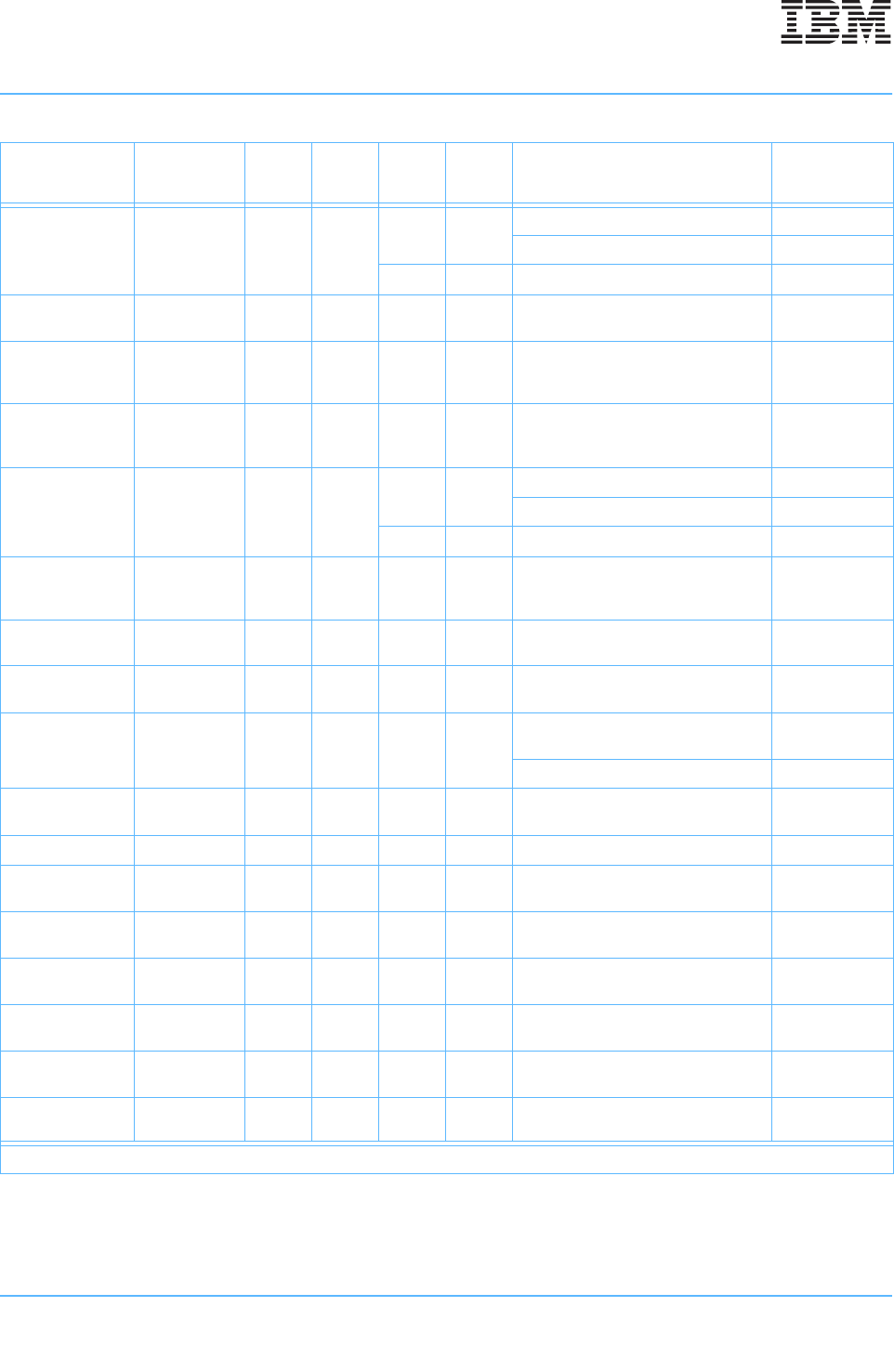

dcbst

Data-cache-

block store

No xxx

I,E Same

dcbst. —

Pass clean. Clean

Same Same No action. —

dcbst

Data-cache-

block store

No xxx M E Push block to write queue. Write-with-kill

dcbz

Data-cache-

block set to

zero

No x1x x x Alignment trap. —

dcbz

Data-cache-

block set to

zero

No 10x x x Alignment trap. —

dcbz

Data-cache-

block set to

zero

Yes 00x

ISame

Cast out of modified block. Write-with-kill

Pass kill. Kill

Same M Clear block. —

dcbz

Data-cache-

block set to

zero

No 00x E,M M Clear block. —

dcbt

Data-cache-

block touch

No x1x I Same

Pass single-beat read to memory

queue.

Read

dcbt

Data-cache-

block touch

No x1x M I Push block to write queue. Write-with-kill

dcbt

Data-cache-

block touch

No x0x I Same

Cast out of modified block (as

required).

Write-with-kill

Pass 4-beat read to memory queue. Read

dcbt

Data-cache-

block touch

No x0x E,M Same No action. —

Single-beat read Reload dump 1 No xxx I Same Forward data_in. —

4-beat read (dou-

ble-word-aligned)

Reload dump No xxx I E Write data_in to cache. —

4-beat write (dou-

ble-word-aligned)

Reload dump No xxx I M Write data_in to cache. —

E

→I

Snoop

write or kill

No xxx E I State change only (committed). —

M

→I

Snoop

kill

No xxx M I State change only (committed). —

Push

M

→I

Snoop

flush

No xxx M I Conditionally push. Write-with-kill

Push

M

→E

Snoop

clean

No xxx M E Conditionally push. Write-with-kill

Table 3-7. MEI State Transitions (Page 2 of 3)

Operation

Cache

Operation

Bus

Sync

WIM

Current

Cache

State

Next

Cache

State

Cache Actions Bus Operation

Note: Single-beat writes are not snooped in the write queue.