User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_03.fm.(1.2)

March 27, 2006

Instruction-Cache and Data-Cache Operation

Page 141 of 377

3.6.2 Bus Operations Caused by Cache-Control Instructions

The cache-control, TLB management, and synchronization instructions supported by the 750GX can affect or

be affected by the operation of the 60x bus. The operation of the instructions can also indirectly cause bus

transactions to be performed, or their completion can be linked to the bus.

The dcbz instruction is the only cache-control instruction that causes an address-only broadcast on the 60x

bus. All other data cache-control instructions (dcbi, dcbf, dcbst, and dcbz) are not broadcast unless specifi-

cally enabled through the HID0[ABE] configuration bit. Note that dcbi, dcbf, dcbst, and dcbz do broadcast to

the 750GX’s L2 cache, regardless of HID0[ABE]. HID0[ABE] also controls the broadcast of the sync and

Enforce In-Order Execution of I/O (eieio) instructions.

The icbi instruction is never broadcast. No broadcasts by other masters are snooped by the 750GX (except

for dcbz kill block transactions). For detailed information on the cache-control instructions, see Chapter 2,

Programming Model, on page 57.

Table 3-4 provides an overview of the bus operations initiated by cache-control instructions. Note that the

information in this table assumes that the WIM bits are set to 001; that is, the cache is operating in write-back

mode, caching is enabled and coherency is enforced.

For additional details about the specific bus operations performed by the 750GX, see Chapter 8, Bus Inter-

face Operation, on page 279 in this manual.

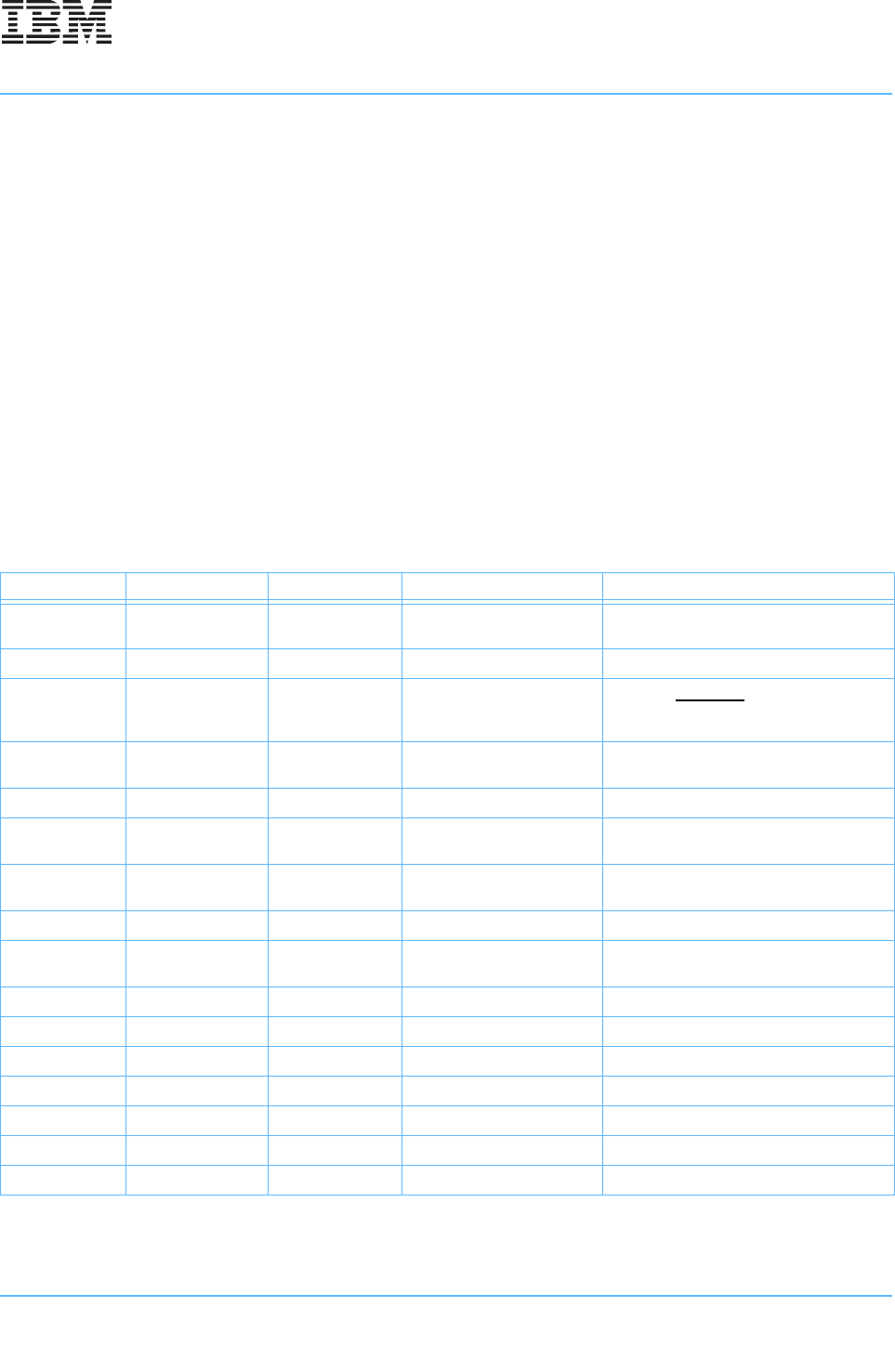

Table 3-4. Bus Operations Caused by Cache-Control Instructions (WIM = 001)

Instruction Current Cache State Next Cache State Bus Operation Comment

sync Don’t care No change

sync

(if enabled in HID0[ABE])

Waits for memory queues to complete bus

activity.

tlbie — — None TLB invalidate entry.

tlbsync — — None

TLB synchronization. Waits for the nega-

tion of the TLBSYNC

input signal to com-

plete.

eieio Don’t care No change

eieio

(if enabled in HID0[ABE])

Address-only bus operation.

icbi Don’t care I None —

dcbi Don’t care I

Kill block

(if enabled in HID0[ABE])

Address-only bus operation.

dcbf I, E I

Flush block

(if enabled in HID0[ABE])

Address-only bus operation.

dcbf M I Write with kill Block is pushed.

dcbst I, E No change

Clean block

(if enabled in HID0[ABE])

Address-only bus operation.

dcbst M E Write with kill Block is pushed.

dcbz I M Write with kill —

dcbz E, M M Kill block Writes over modified data.

dcbt I E Read-with-intent-to-modify Fetched cache block is stored in the cache.

dcbt E, M No change None —

dcbtst I E Read-with-intent-to-modify Fetched cache block is stored in the cache.

dcbtst E,M No change None —