User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

PowerPC 750GX Overview

Page 50 of 377

gx_01.fm.(1.2)

March 27,2006

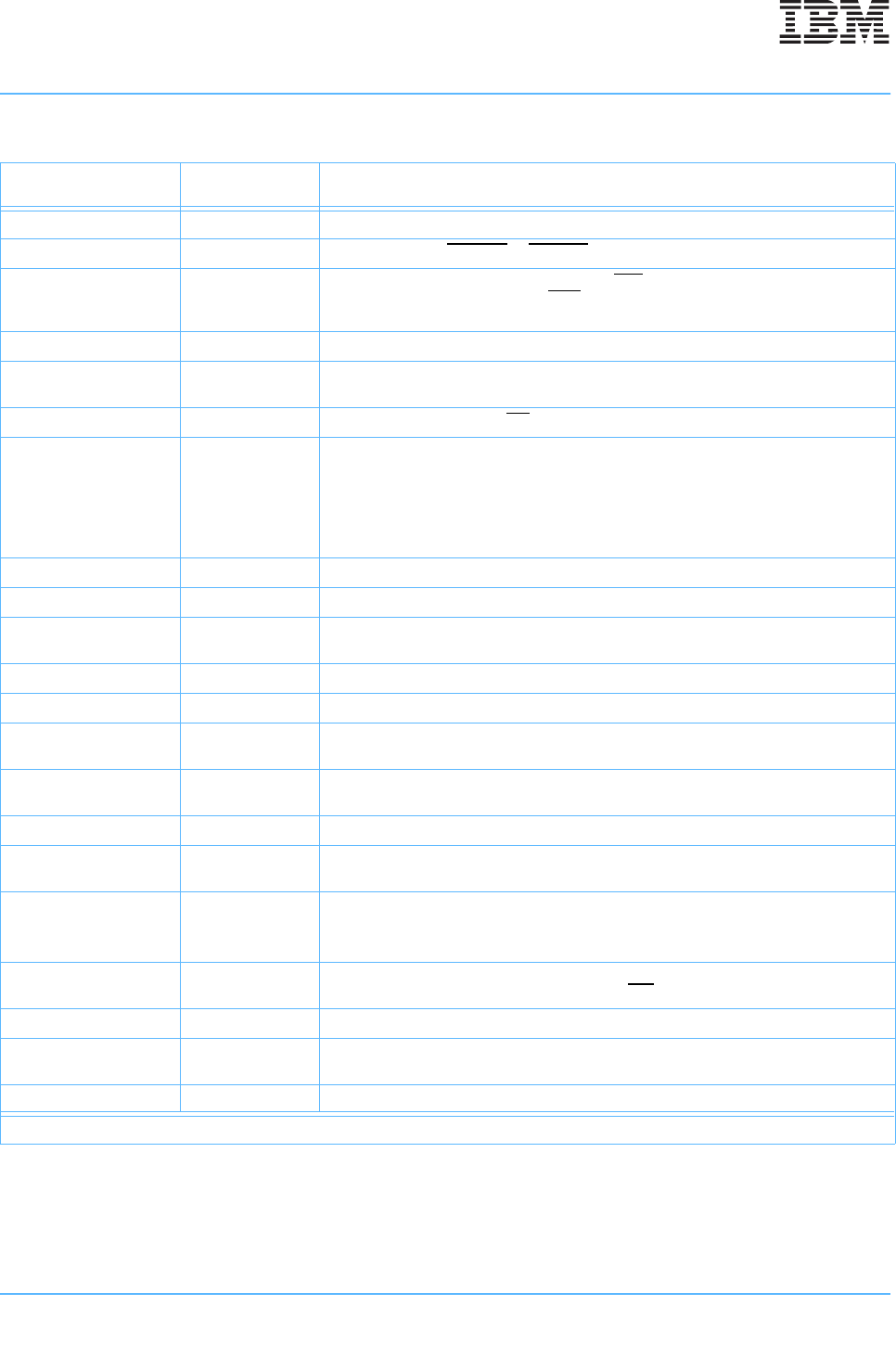

Table 1-5. Exceptions and Conditions

Exception Type

Vector Offset

(hex)

Causing Conditions

Reserved 00000 —

System reset 00100 Assertion of either HRESET

or SRESET or a power-on reset.

Machine check 00200

Assertion of the transfer error acknowledge (T

EA) during a data-bus transaction, asser-

tion of a machine-check interrupt (MCP

), an address, data or L2 double-bit error.

MSR[ME] must be set.

Data storage interrupt 00300 As defined in the PowerPC Architecture (for example, a page fault occurs).

Instruction storage inter-

rupt (ISI)

00400 As defined by the PowerPC Architecture (for example, a page fault occurs).

External interrupt 00500 MSR[EE] = 1 and interrupt (INT

) is asserted.

Alignment 00600

• A floating-point load/store, Store Multiple Word (stmw), Store Word Conditional

Indexed (stwcx.), Load Multiple Word (lmw), Load Word and Reserved Indexed

(lwarx), eciwx, or ecowx instruction operand is not word-aligned.

• A multiple/string load/store operation is attempted in little-endian mode.

• The operand of Data Cache Block Zero (dcbz) is in memory that is write-through-

required or caching-inhibited, or the cache is disabled.

Program 00700 As defined by the PowerPC Architecture.

Floating-point unavailable 00800 As defined by the PowerPC Architecture.

Decrementer 00900

As defined by the PowerPC Architecture, when the most significant bit of the DEC reg-

ister changes from 0 to 1 and MSR[EE] = 1.

Reserved 00A00–00BFF —

System call 00C00 Execution of the System Call (sc) instruction.

Trace 00D00

MSR[SE] = 1 or a branch instruction completes and MSR[BE] = 1. Unlike the architec-

ture definition, Instruction Synchronization (isync) does not cause a trace exception

Reserved 00E00

The 750GX does not generate an exception to this vector. Other PowerPC processors

might use this vector for floating-point assist exceptions.

Reserved 00E10–00EFF —

Performance monitor

1

00F00

The limit specified in a Performance-Monitor Control (PMC) register is reached and

MMCR0[ENINT] = 1.

Instruction address

breakpoint

1

01300

IABR[0–29] matches EA[0–29] of the next instruction to complete,

IABR[TE] matches MSR[IR], and

IABR[BE] = 1.

System management

exception

01400

A system management exception is enabled if MSR[EE] = 1 and is signaled to the

750GX by the assertion of an input signal pin (SMI

).

Reserved 01500–016FF —

Thermal-management

interrupt

1

01700

Thermal management is enabled, the junction temperature exceeds the threshold

specified in THRM1 or THRM2, and MSR[EE] = 1.

Reserved 01800–02FFF —

1. 750GX-specific