User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_02.fm.(1.2)

March 27, 2006

Programming Model

Page 111 of 377

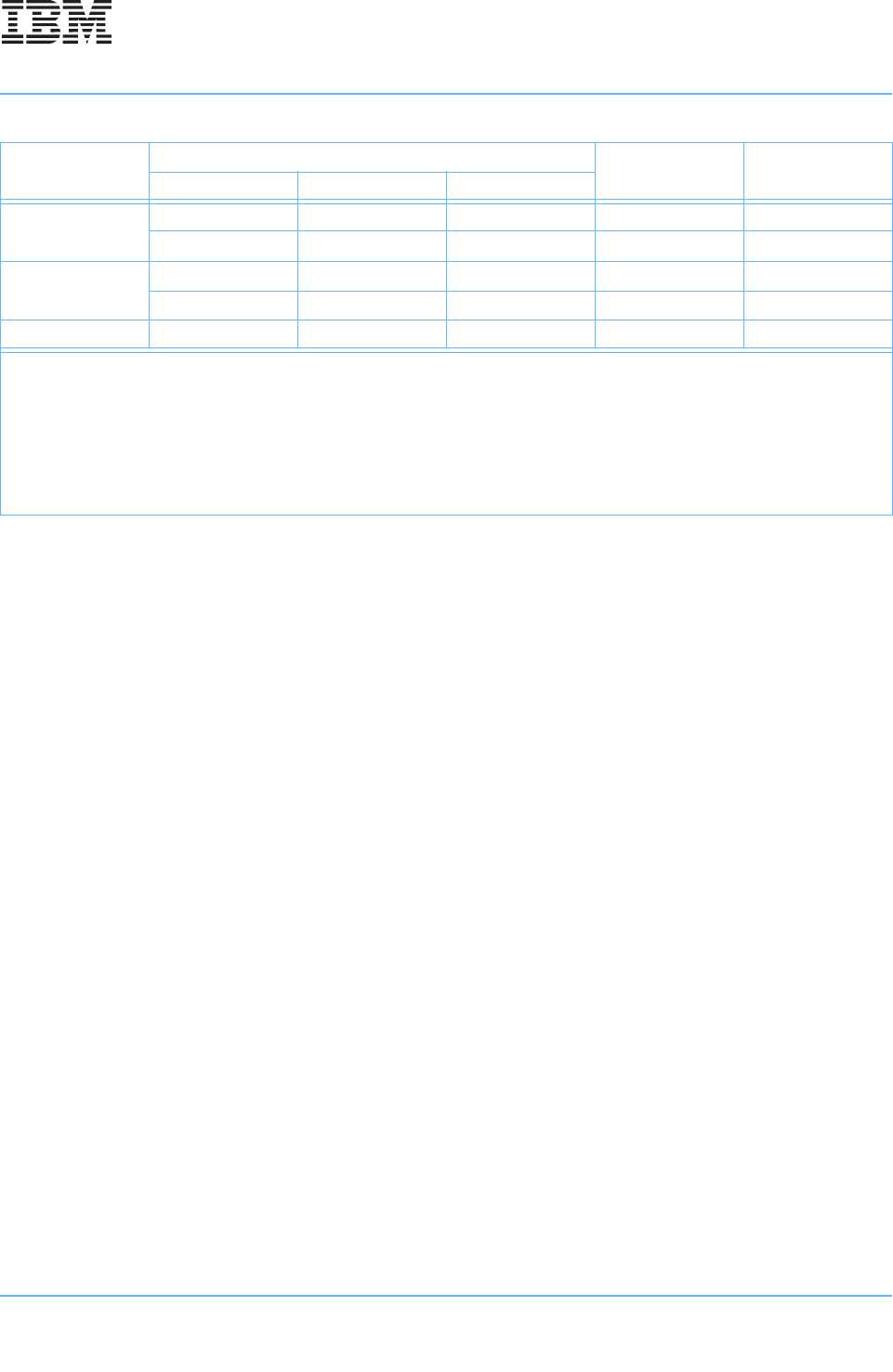

TBL

2

268 01000 01100 User (VEA) mfspr

284 01000 11100 Supervisor (OEA) mtspr

TBU

2

269 01000 01101 User (VEA) mfspr

285 01000 11101 Supervisor (OEA) mtspr

XER 1 00000 00001 User (UISA) Both

Table 2-33. PowerPC Encodings (Page 3 of 3)

Register Name

SPR

1

Access mfspr/mtspr

Decimal SPR[5–9] SPR[0–4]

Note:

1. The order of the two 5-bit halves of the SPR number is reversed compared with actual instruction coding. For mtspr and mfspr

instructions, the SPR number coded in assembly language does not appear directly as a 10-bit binary number in the instruction.

The number coded is split into two 5-bit halves that are reversed in the instruction, with the high-order five bits appearing in bits

16–20 of the instruction and the low-order five bits in bits 11–15.

2. The TB Registers are referred to as TBRs rather than SPRs and can be written to using the mtspr instruction in supervisor mode

and the TBR numbers here. The TB Registers can be read in user mode using either the mftb or mfspr instruction and specifying

TBR 268 for TBL and SPR 269 for TBU.