User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction-Cache and Data-Cache Operation

Page 140 of 377

gx_03.fm.(1.2)

March 27, 2006

Burst transactions on the 750GX always transfer eight words of data at a time, and are aligned to a double-

word boundary. The 750GX transfer burst (TBST

) output signal indicates to the system whether the current

transaction is a single-beat transaction or 4-beat burst transfer. Burst transactions have an assumed address

order. For cacheable read operations, instruction fetches, or cacheable, non-write-through write operations

that miss the cache, the 750GX presents the double-word-aligned address associated with the load/store

instruction or instruction fetch that initiated the transaction.

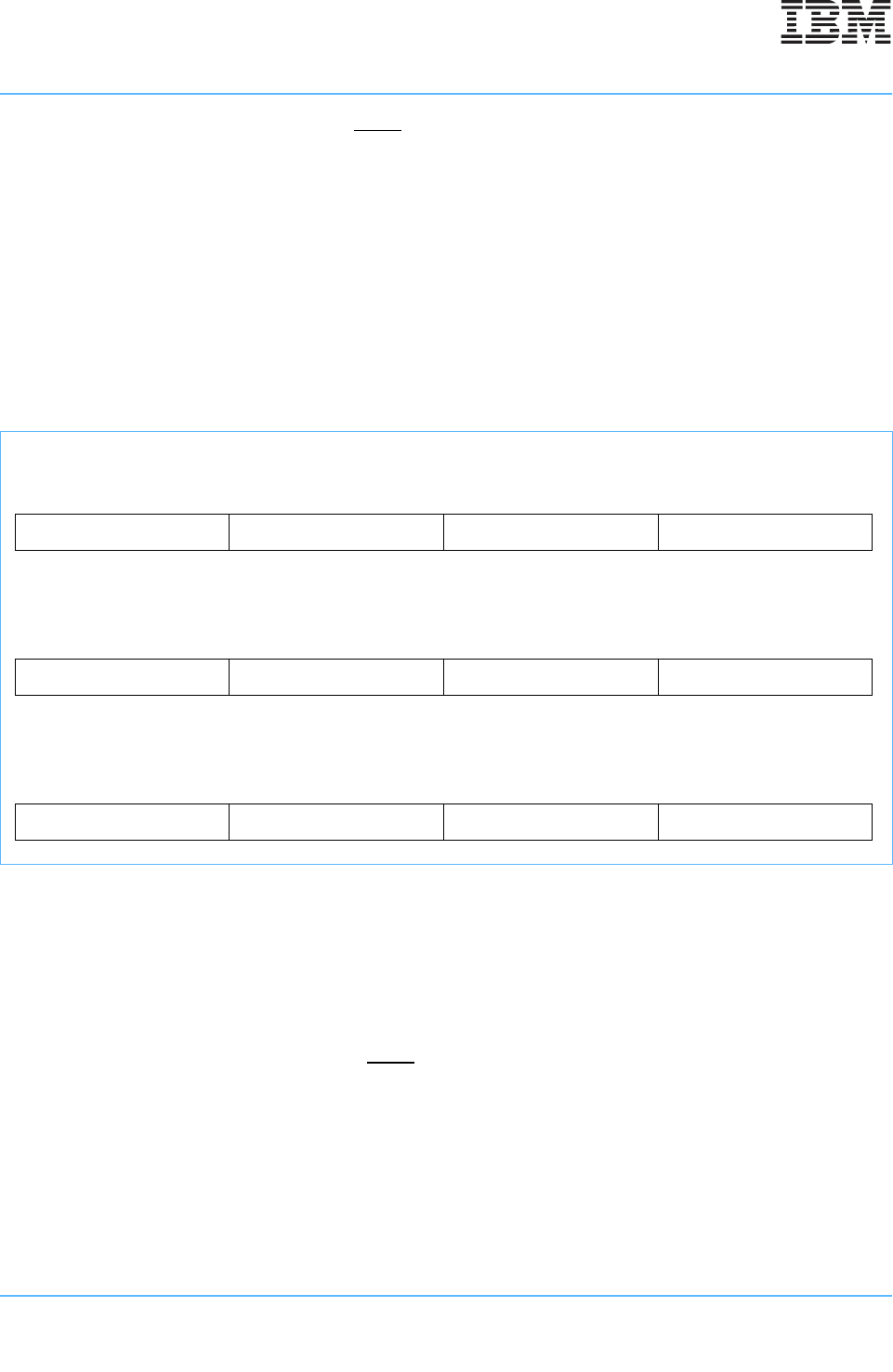

As shown in Figure 3-6, the first quadword contains the address of the load/store or instruction fetch that

missed the cache. This minimizes latency by allowing the critical code or data to be forwarded to the

processor before the rest of the block is filled. For all other burst operations, however, the entire block is

transferred in order. Critical-double-word-first fetching on a cache miss applies to both the data and instruc-

tion cache.

3.6.1 Read Operations and the MEI Protocol

The MEI coherency protocol affects how the 750GX data cache performs read operations on the 60x bus. All

reads (except for caching-inhibited reads) are encoded on the bus as read-with-intent-to-modify (RWITM) to

force flushing of the addressed cache block from other caches in the system.

The MEI coherency protocol also affects how the 750GX snoops read operations on the 60x bus. All reads

snooped from the 60x bus (except for caching-inhibited reads) are interpreted as RWITM to cause flushing

from the 750GX’s cache. Single-beat reads (TBST

negated) are interpreted by the 750GX as caching inhib-

ited.

These actions for read operations allow the 750GX to operate successfully (coherently) on the bus with other

bus masters that implement either the 3-state MEI or a 4-state MESI cache-coherency protocol.

Figure 3-6. 750GX Cache Addresses

If the address requested is in double-word A, the address placed on the bus is that of double-word A, and the four data

beats are ordered in the following manner:

If the address requested is in double-word C, the address placed on the bus will be that of double-word C, and the four

data beats are ordered in the following manner:

ABCD

111000 01

ABCD

3201

Beat

Bits (27... 28)

CDAB

3201

Beat

750GX Cache Address