User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction Timing

Page 238 of 377

gx_06.fm.(1.2)

March 27, 2006

• Requirements for completing an instruction from CQ1:

– Instruction in CQ0 must complete in same cycle.

– Instruction in CQ1 must be finished.

– Instruction in CQ1 must not follow an unresolved predicted branch.

– Instruction in CQ1 must not cause an exception.

– Instruction in CQ1 must be an integer or load instruction.

– Number of CR updates from both CQ0 and CQ1 must not exceed two.

– Number of GPR updates from both CQ0 and CQ1 must not exceed two.

– Number of FPR updates from both CQ0 and CQ1 must not exceed two.

6.7 Instruction Latency Summary

Table 6-4 through Table 6-9 list the latencies associated with instructions executed by each execution unit.

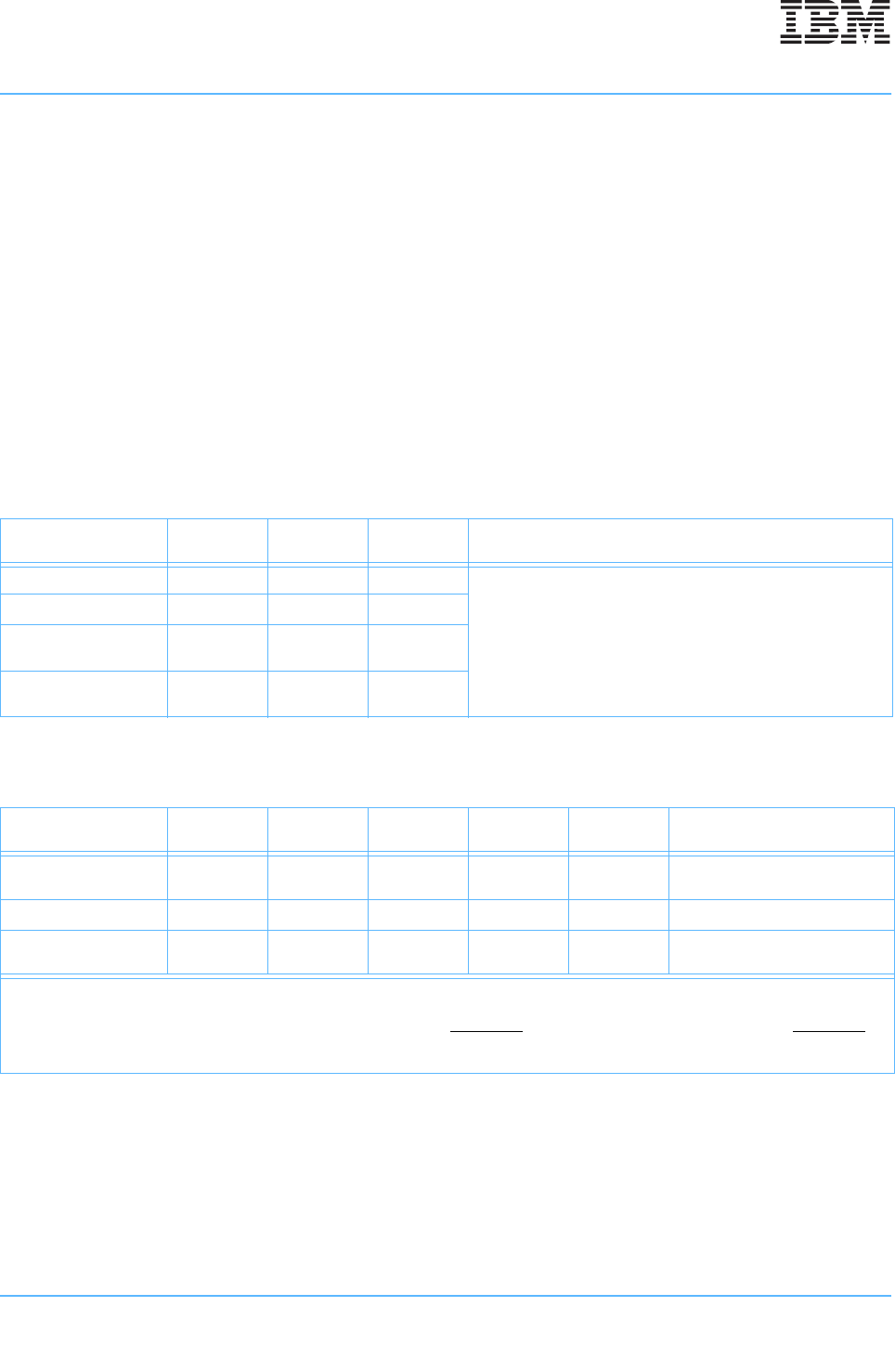

Table 6-4 describes branch instruction latencies.

Table 6-5 lists system-register instruction latencies.

Table 6-4. Branch Instructions

Instruction Mnemonic

Primary

Opcode

Extended

Opcode

Latency

Branch b[l][a] 18 —

Unless these instructions update either the CTR or the LR,

branch operations are folded if they are either taken or pre-

dicted as taken. They fall through if they are not taken or pre-

dicted as not taken.

Branch Conditional bc[l][a] 16 —

Branch Conditional to

Count Register

bcctr[l] 19 528

Branch Conditional to

Link Register

bclr[l] 19 16

Table 6-5. System-Register Instructions (Page 1 of 2)

Instruction Mnemonic

Primary

Opcode

Extended

Opcode

Unit Cycles Serialization

Enforce In-Order

Execution of I/O

eieio 31 854 SRU 1 —

Instruction Synchronize isync 19 150 SRU 2 Completion, refetch

Move-from Machine

State Register

mfmsr 31 83 SRU 1 —

1. This 3-cycle operation assumes no pending stores in the store queue. If there are pending stores, the sync completes after the

stores complete to memory. If broadcast is enabled on the 60x bus, sync completes only after a successful broadcast.

2. tlbsync is dispatched only to the completion buffer (not to any execution unit) and is marked finished as it is dispatched. Upon

retirement, it waits for an external TLB Invalidate Synchronize (TLBISYNC

) signal to be asserted. In most systems, TLBISYNC is

always asserted so the instruction is a no-op.