User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_02.fm.(1.2)

March 27, 2006

Programming Model

Page 115 of 377

2.3.5.3 Memory Control Instructions—VEA

Memory control instructions can be classified as follows:

• Cache-management instructions (user-level and supervisor-level)

• Segment Register manipulation instructions (OEA)

• Translation-lookaside-buffer management instructions (OEA)

This section describes the user-level cache-management instructions defined by the VEA. See

Section 2.3.6.3 on page 119 for information about supervisor-level cache, Segment Register manipulation,

and translation lookaside buffer management instructions.

User-Level Cache Instructions—VEA

The instructions summarized in this section help user-level programs manage on-chip caches if they are

implemented. See Chapter 3, Instruction-Cache and Data-Cache Operation, on page 121 for more informa-

tion about cache topics. The following sections describe how these operations are treated with respect to the

750GX’s cache.

As with other memory-related instructions, the effects of cache-management instructions on memory are

weakly-ordered. If the programmer must ensure that cache or other instructions have been performed with

respect to all other processors and system mechanisms, a sync instruction must be placed after those

instructions.

Note that the 750GX interprets cache-control instructions (icbi, dcbi, dcbf, dcbz, and dcbst) as if they

pertain only to the local L1 and L2 cache. A dcbz (with M set) is always broadcast on the 60x bus. The dcbi,

dcbf, and dcbst operations are broadcast if HID0[ABE] is set.

The 750GX never broadcasts an icbi. Of the broadcast cache operations, the 750GX snoops only dcbz,

regardless of the HID0[ABE] setting. Any bus activity caused by other cache instructions results directly from

performing the operation on the 750GX cache. All cache-control instructions to a direct-store segment

(SR[T] = 1 space) are no-ops. For information on how cache-control instructions affect the L2, see Chapter 9,

L2 Cache, on page 323.

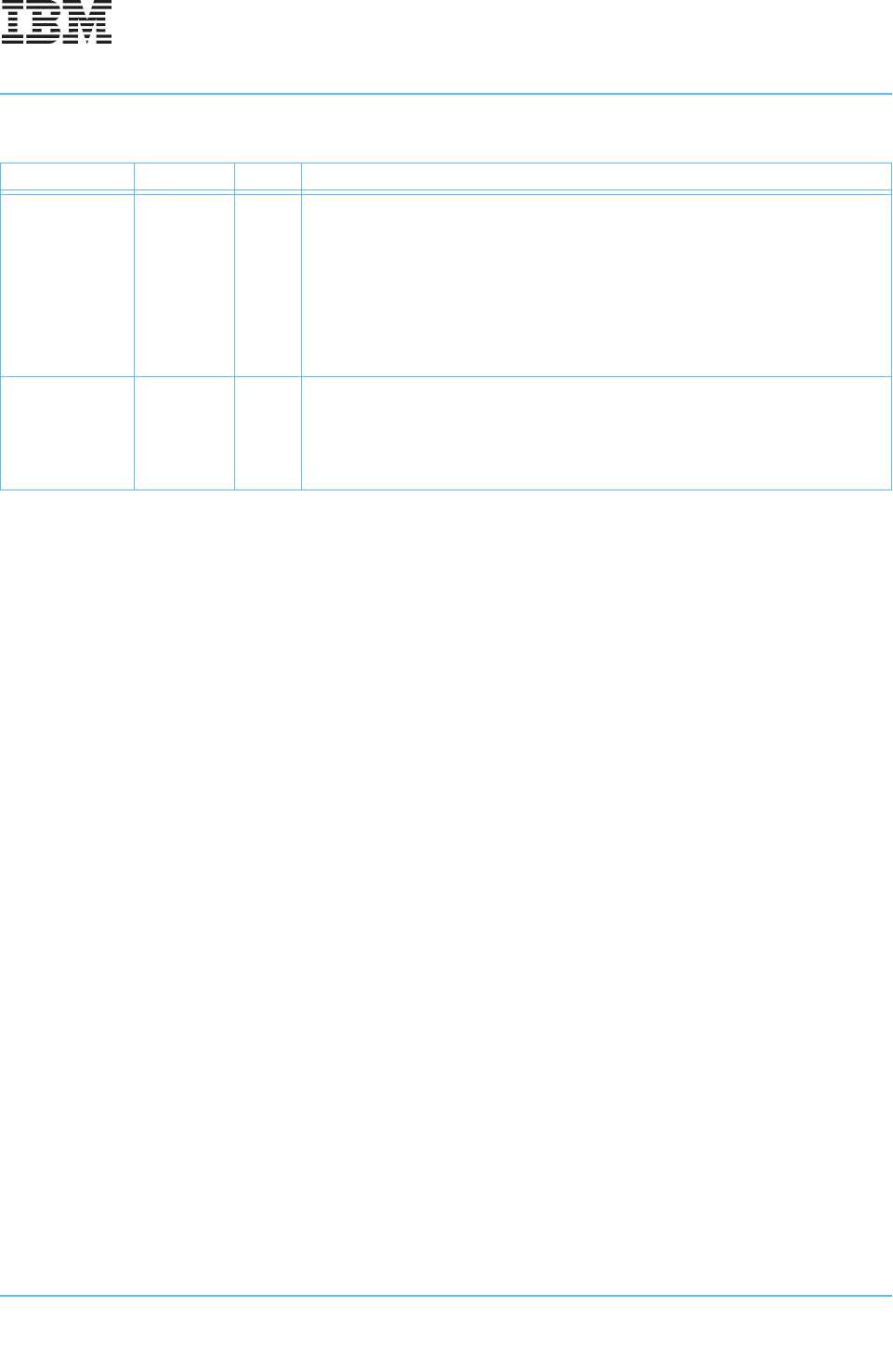

Table 2-37. Memory Synchronization Instructions—VEA

Name Mnemonic Syntax Implementation Notes

Enforce In-Order

Execution of I/O

eieio —

The eieio instruction is dispatched to the LSU and executes after all previous cache-

inhibited or write-through accesses are performed. All subsequent instructions that gen-

erate such accesses execute after eieio. If HID0[ABE] = 1, an EIEIO operation is broad-

cast on the external bus to enforce ordering in the external memory system. The eieio

operation bypasses the L2 cache and is forwarded to the bus unit. If HID0[ABE] = 0, the

operation is not broadcast.

Because the 750GX does not reorder noncacheable accesses, eieio is not needed to

force ordering. However, if store gathering is enabled and an eieio is detected in a store

queue, stores are not gathered. If HID0[ABE] = 1, broadcasting eieio prevents external

devices, such as a bus bridge chip, from gathering stores.

Instruction

Synchronize

isync —

The isync instruction is refetch serializing. That is, it causes the 750GX to purge its

instruction queue and wait for all prior instructions to complete before refetching the next

instruction, which is not executed until all previous instructions complete to the point

where they cannot cause an exception. The isync instruction does not wait for all pend-

ing stores in the store queue to complete. Any instruction after an isync sees all effects

of prior instructions.