User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Memory Management

Page 198 of 377

gx_05.fm.(1.2)

March 27, 2006

• Accesses that cause exceptions and are not completed.

5.4.1.2 Changed Bit

The changed bit of a page is located both in the PTE in the page table and in the copy of the PTE loaded into

the TLB (if a TLB is implemented, as in the 750GX). Whenever a data store instruction is executed success-

fully, if the TLB search (for page-address translation) results in a hit, then the changed bit in the matching TLB

entry is checked. If it is already set, it is not updated. If the TLB changed bit is 0, the 750GX initiates the table-

search operation to set the C bit in the corresponding PTE in the page table. The 750GX then reloads the

TLB (with the C bit set).

The changed bit (in both the TLB and the PTE in the page tables) is set only when a store operation is

allowed by the page memory-protection mechanism and the store is guaranteed to be in the execution path

(unless an exception, other than those caused by the sc, rfi, or trap instructions, occurs). Furthermore, the

following conditions can cause the C bit to be set:

• The execution of an stwcx. instruction is allowed by the memory-protection mechanism but a store oper-

ation is not performed.

• The execution of an stswx instruction is allowed by the memory-protection mechanism but a store opera-

tion is not performed because the specified length is zero.

• The store operation is not performed because an exception occurs before the store is performed.

Again, note that although the execution of the dcbt and dcbtst instructions might cause the R bit to be set,

they never cause the C bit to be set.

5.4.1.3 Scenarios for Referenced and Changed Bit Recording

This section provides a summary of the model (defined by the OEA) that is used by PowerPC processors for

maintaining the referenced and changed bits. In some scenarios, the bits are guaranteed to be set by the

processor; in some scenarios, the architecture allows the bits to be set (not absolutely required); and in some

scenarios, the bits are guaranteed to not be set. Note that when the 750GX updates the R and C bits in

memory, the accesses are performed as if MSR[DR] = 0 and G = 0 (that is, as nonguarded cacheable opera-

tions in which coherency is required).

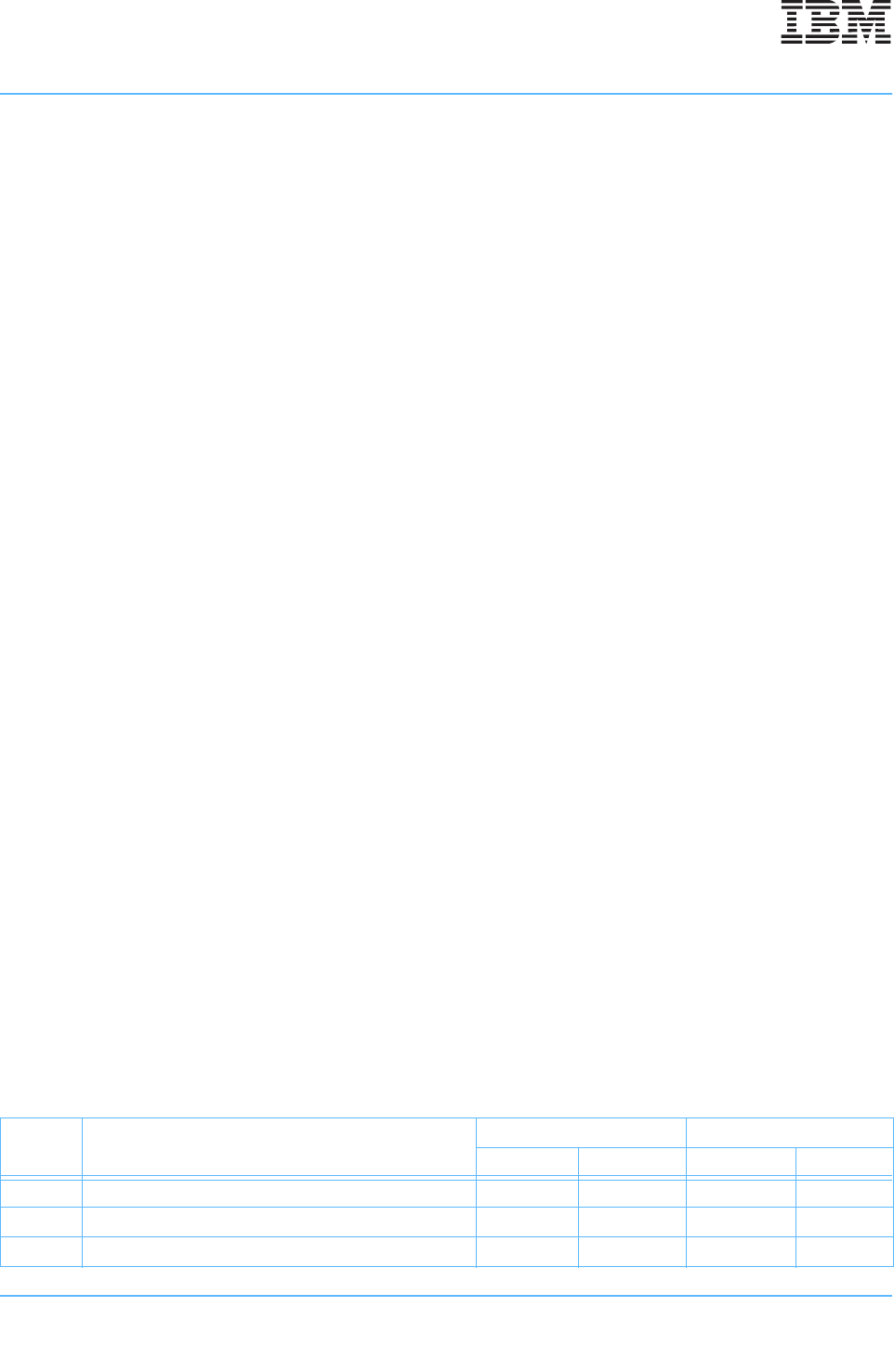

Table 5-8 on page 198 defines a prioritized list of the R and C bit settings for all scenarios. The entries in the

table are prioritized from top to bottom, so that a scenario near the top of the table takes precedence over a

scenario near the bottom of the table. For example, if an stwcx. instruction causes a page-protection violation

and there is no reservation, the C bit is not altered. Note that in the table, load operations include those

generated by load instructions, by the eciwx instruction, and by the cache-management instructions that are

treated as a load with respect to address translation. Similarly, store operations include those operations

generated by store instructions, by the ecowx instruction, and by the cache-management instructions that

are treated as a store with respect to address translation.

Table 5-8. Model for Guaranteed R and C Bit Settings

(Page 1 of 2)

Priority Scenario

Causes Setting of R Bit Causes Setting of C Bit

OEA 750GX OEA 750GX

1 No-execute protection violation No No No No

2 Page-protection violation Maybe Yes No No

3 Out-of-order instruction fetch or load operation Maybe No No No