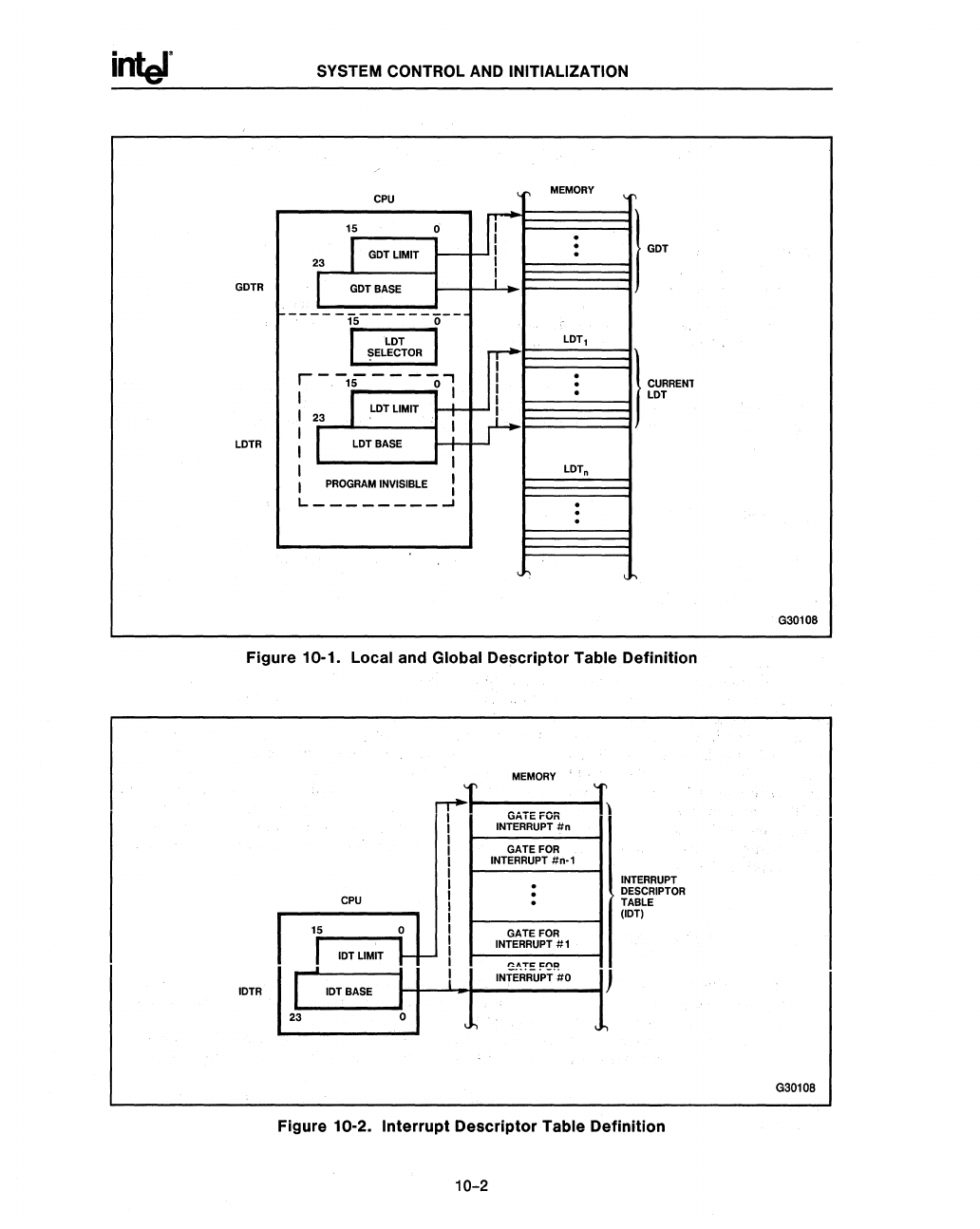

SYSTEM CONTROL

AND

INITIALIZATION

MEMORY

CPU

,

GDTR

U!

15

0

·

J

-

·

GDTLIMIT

·

23 I

I

GDTBASE

I

--

15

0--

1

CURRENl

LDT

I LDT

LDTl

~ELECTOR

I

r-------.,

I

·

15 0 I

I

·

I

·

I

i

I

I

LDTLIMIT

-I

23

I

I

i

..J

I

LDTBASE

I

LDT

n

I

PROGRAM

INVISIBLE

I

I

LDTR

L

________

....I

·

·

·

,~

Figure 10-1. Local and Global

Descriptor

Table Definition

IDTR

!

CPU

o~

15

J

IDTLIMIT

I

IDT BASE

i

23

0

MEMORY

GATE

FOR

INTERRUPT

#n

GATE

FOR

INTERRUPT

#"-1

·

·

·

GATE

FOR

INTERRUPT

#1

~~T!:!=~~

INTERRUPT

#0

\

J

,.,

INTERRUPT

DESCRIPTOR

TABLE

(lDT)

Figure 10-2.

Interrupt

Descriptor

Table Definition

10-2

G3010B

G3010B