des.

limit

bale_low

b a

I!_h

I g h

a

••

ess

res

des.

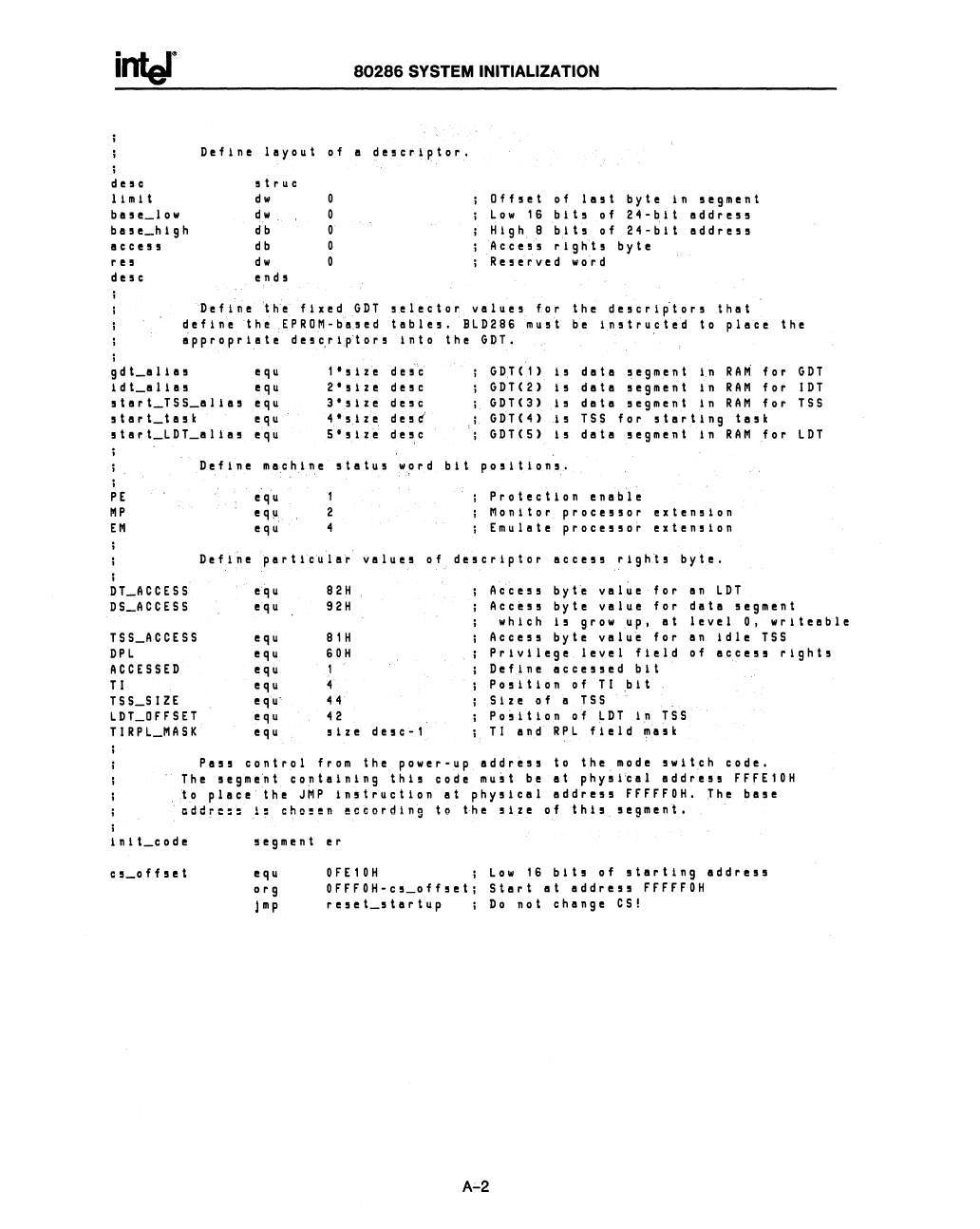

80286

SYSTEM INITIALIZATION

Define

layout

of

a

desc~l~tor!

s t r u c

dw

dw

db

db

dw

ends

Offset

of

last

byte

In

segment

Low

16

bits

of

24-blt

address

Hlgh,8

bit.

of

24-blt

addrels

,Access

rlg~tl

byte

Reserved

wo'rd

'D

e

fin

e 't

h'e'

fixe

d G D T

I!

I e c

tor,

val

u e s

1.

0 r

the

des

c

rip'

tors

,t

hat

de

fin

e

't

hO

EP

ROM

-

ba,l!

d

tab

I e

I.

B L D 2

86m

us

t be

in.

t r u

,c

ted

top

I

ace

the

~pproprlat.

des~rl~tors

Int,o

the

GDT.

gdt_allas

equ

I

"s

I

z'e

des

'c

GDT

(I)

I I

date

segm,ent

I,n

RAM'

for

I d

t_alla.

equ

2"slze

desc

GDH2)

I.

data

segment

In

RAM

for

s

tar

t_

T S

S_a

I I a s

equ

3"slze

desc

GDH3)

Is

data

segment

In

RAM

for

s

tar

t_

t a I •

equ

4,.

1,1

z

e,

des

cf

.,

GDH4)

I.

TSS

for

starting

ta

••

s

tar

t_L

D T

_a

I I

BI

e

q'u

5 " s,l

z!

desc

GDHS)

Is

da

te

segment

I

n,

RAM

for

Define

machine

Itatus

word

bit

pOs'ltlonS,..

PE

MP

EM

DT_ACCESS

DS_ACCESS

I

2

4

Pro

t e c t

Ion

en

ab

'I

e

Monitor

procelsor

extension

Emulate

procelsor

extension

Defl~e

)artl~.ia~

values

of

de.crlptor

acce~Irlghts

byte.

equ

82,H

Access

byh

value

for

an

LDT

equ

92H

Acce.s

byte

value

for

date

segment

GDT

IDT

TSS

LDT

which

Is

g row

.u

p.

at

level

o •

wrlteable

TS

LA

C C E S S

DPL

ACCESSED

T I

TSS_SIZE

LDT_OFFSET

T

1R

P

L_MA

S K

equ

equ

equ

equ

e

q'u"

equ

equ

81H

60H

I

4

44

42

• I z e

desc-I

.

Access

byte

val

u'e

for

an

I

die

TSS

Privilege

level

f1

e

I,d

of

a

c,c

e.

s

rights

Define

acces.ed

bit

Position

of

T I

bit

Size

of

a

TSS

Position

of

LDT

In

TSS

T I

end

RPL

f1

e I d

~alk

Pass

contr~1

from

the

power-up

addresl

to

the

mode

Iwltch

code.

The

segme~t

containing

thll

code

must

be

at

phy~l~al

address

FFFEIOH

.to

place

~he

JMP

Inltructlon

a~

phySical

add~ess

FFFFFOH.

Jhe

base

'cddr:~~

!~

chosen

eC~Drdln~

t.

the

size

of

this

segment.

cs_offlet

legment

er

equ

org

jmp

OFEIOH

Low

16

bits

of

starting

address

OFFFOH-cs_offset;

Start

at

addresl

FFFFFOH

Do

not

change

CS!