THE

80286

INSTRUCTION SET

LGDT

ILIDT

-Load

Global/Interrupt

Descriptor Table Register

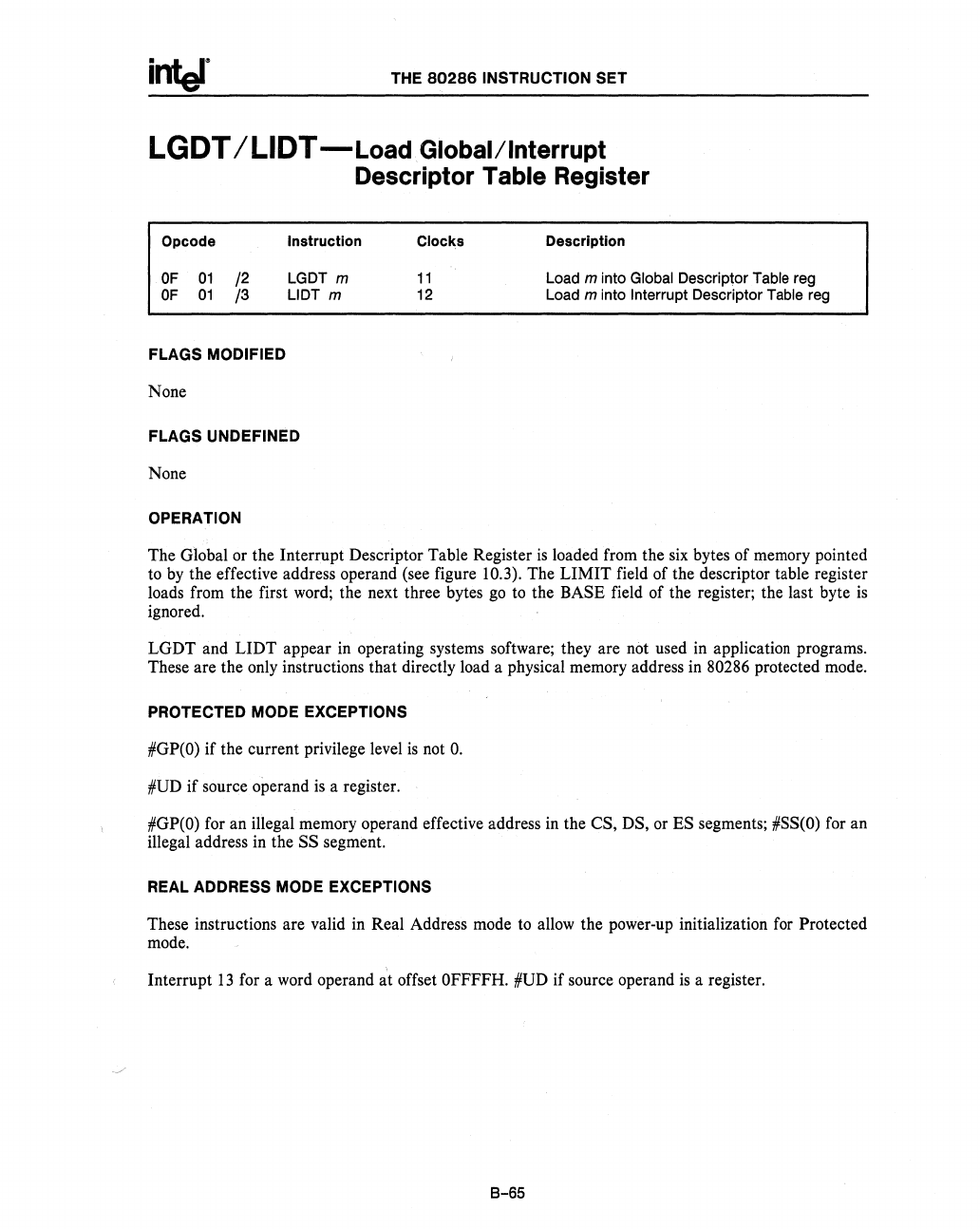

Opcode

OF

01

/2

OF

01

/3

FLAGS MODIFIED

None

Instruction

LGDT m

LlDT m

FLAGS UNDEFINED

None

OPERATION

Clocks

11

12

Description

Load m into Global Descriptor Table reg

Load

m into Interrupt Descriptor Table reg

The Global or the Interrupt Descriptor Table Register

is

loaded from the

six

bytes of memory pointed

to by the effective address operand (see figure 10.3). The LIMIT field of the descriptor table register

loads from the first word; the next three bytes

go

to the BASE field of the register; the last byte

is

ignored.

LGDT and LIDT appear

in

operating systems software; they are not used

in

application programs.

These are the only instructions that directly load a physical memory address

in

80286 protected mode.

PROTECTED MODE EXCEPTIONS

#GP(O)

if the current privilege level

is

not

O.

#UD if source operand

is

a register.

#GP(O) for an illegal memory operand effective address

in

the CS, DS,

or

ES segments;

#SS(O)

for an

illegal address in the

SS segment.

REAL ADDRESS MODE EXCEPTIONS

These instructions are valid

in

Real Address mode

to

allow the power-up initialization

for

Protected

mode.

Interrupt

13

for a word operand at offset OFFFFH. #UD if source operand

is

a register.

8-65