inter

I

SS

I

SP

I

80286

BASE

ARCHITECTURE

-

l

+

LOGICAL

BOTTOM OF STACK

(initial SP value)

POP-UP

LOGICAL

TOP OF STACK

PUSH-DOWN

STAC

K SEGMENT BASE ADDRESS

Figure 2-7_

80286

Stack

G3010B

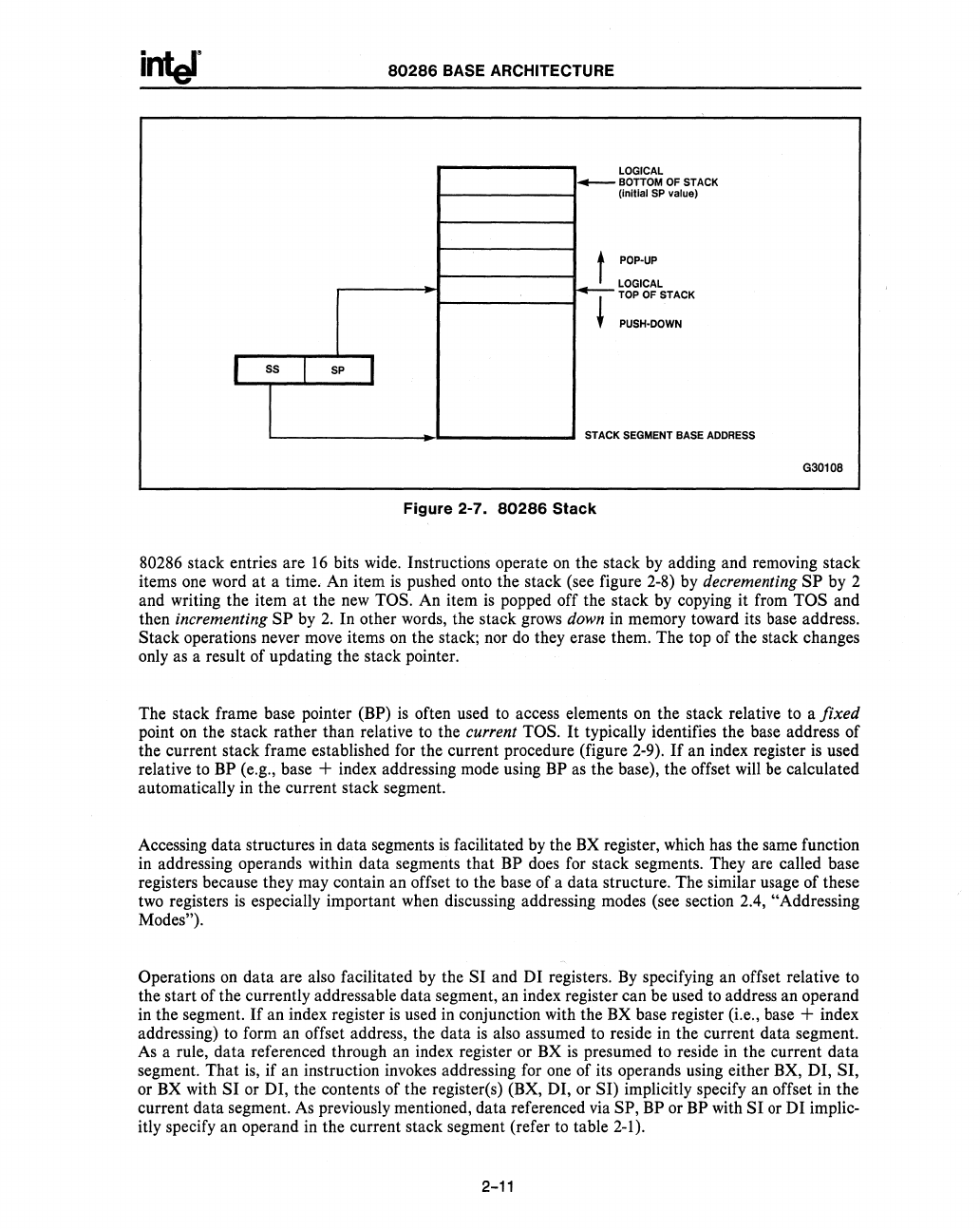

80286 stack entries are

16

bits wide. Instructions operate on the stack

by

adding and removing stack

items one word

at

a time, An item

is

pushed onto the stack (see figure 2-8) by decrementing

SP

by 2

and writing the item

at

the

new

TOS. An item

is

popped off the stack by copying it from TOS and

then

incrementing

SP

by

2.

In other words, the stack grows down in memory toward its base address.

Stack operations never

move

items

on

the stack; nor

do

they erase them. The top of the stack changes

only as a result of updating the stack pointer.

The stack frame base pointer

(BP)

is

often used to access elements on the stack relative to a

fixed

point

on

the stack rather than relative

to

the current TOS.

It

typically identifies the base address of

the current stack frame established for the current procedure (figure 2-9).

If

an index register

is

used

relative

to

BP (e.g., base + index addressing mode using BP as the base), the offset

will

be

calculated

automatically

in

the current stack segment.

Accessing data structures in data segments

is

facilitated

by

the

BX

register, which has the same function

in addressing operands within data segments that

BP does for stack segments. They are called base

registers because they may contain an offset

to

the base of a data structure. The similar usage of these

two

registers

is

especially important when discussing addressing modes (see section 2.4, "Addressing

Modes").

Operations

on

data are also facilitated

by

the SI and DI registers.

By

specifying an offset relative to

the start of the currently addressable data segment, an index register can be used

to

address an operand

in the segment.

If

an index register

is

used in conjunction with the

BX

base register (i.e., base + index

addressing) to form an offset address, the data

is

also assumed to reside in the current data segment.

As

a rule, data referenced through an index register or

BX

is

presumed to reside in the current data

segment. That

is,

if an instruction invokes addressing for

one

of its operands using either BX, DI, SI,

or

BX

with

SI

or DI, the contents of the register(s) (BX, DI, or SI) implicitly specify an offset

in

the

current data segment.

As

previously mentioned, data referenced via SP, BP or BP with

SI

or

DI implic-

itly specify an operand in the current stack segment (refer

to

table

2-1).

2-11