OVERVIEW

OF

NUMERIC PROCESSING

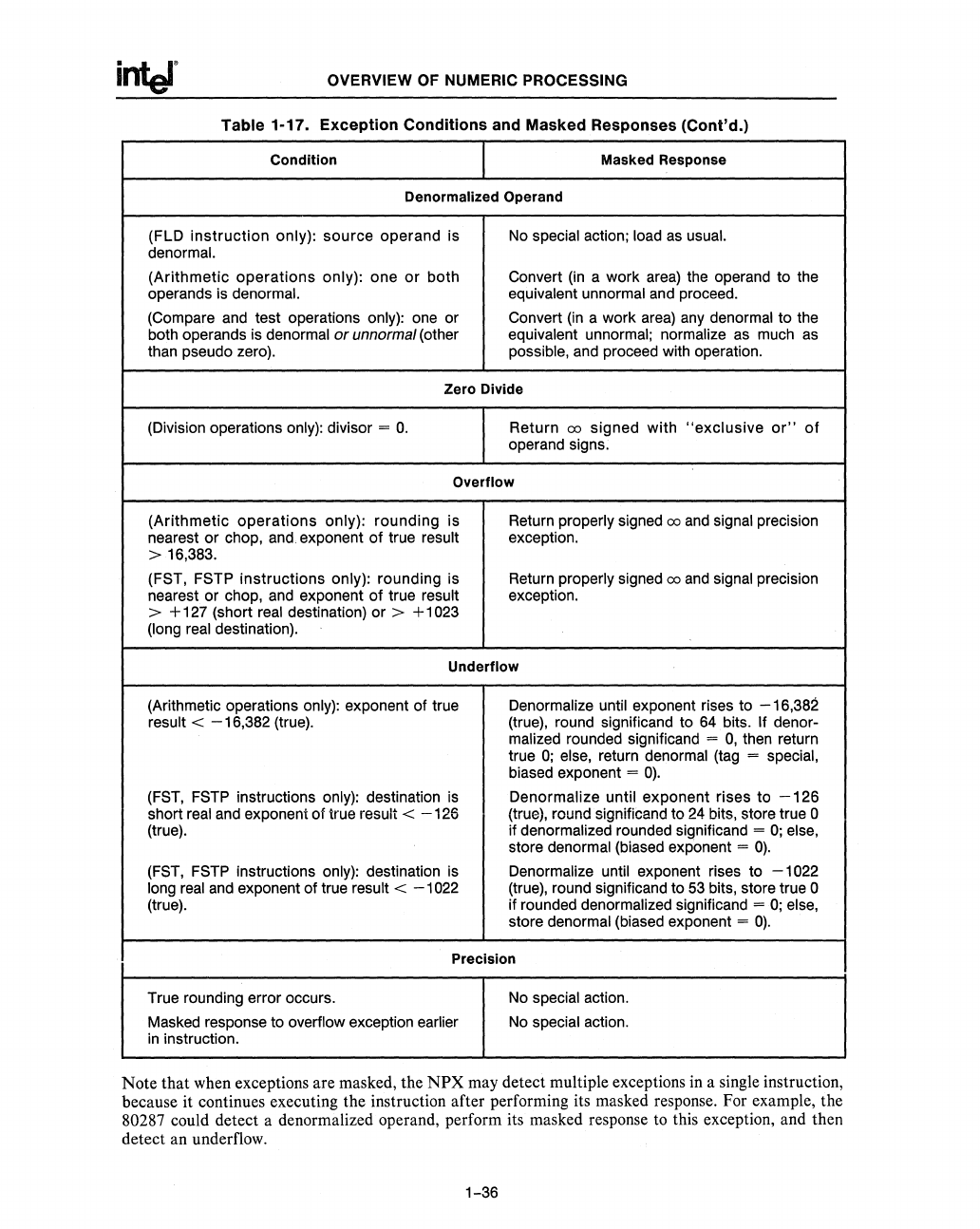

Table

1-17.

Exception

Conditions

and Masked Responses (Cont'd.)

Condition

Masked Response

Denormalized Operand

(FLD

instruction

only): source operand is

No

special action; load

as

usual.

denormal.

(Arithmetic

operations

only): one

or

both

Convert

(in

a work

area)

the operand to the

operands is

denormal. equivalent unnormal and proceed.

(Compare and test operations only): one or Convert

(in

a work area)

any

denormal to the

both operands is denormal

or

unnormal (other equivalent unnormal; normalize

as

much

as

than pseudo zero). possible, and proceed with operation.

Zero Divide

(Division operations only): divisor =

O.

Return

00

signed with

"exclusive

or"

of

operand signs;

Overflow

(Arithmetic

operations

only): rounding is Return properly signed

00

and

signal precision

nearest

or

chop,

and.

exponent

of

true result

exception.

>

16,383.

(FST, FSTP instructions only): rounding is Return properly signed

00

and

Signal

precision

nearest or chop,

and

exponent

of

true result

exception.

>

+127

(short real destination)

or>

+1023

(long real destination).

Underflow

(Arithmetic operations only): exponent of true

Denormalize until exponent rises to

-16,382

result <

-16,382

(true). (true), round significand to 64 bits. If denor-

mali zed rounded significand =

0,

then return

true

0;

else, return denormal (tag = special,

biased exponent

=

0).

(FST,

FSTP

instructions only): destination is Denormalize until exponent rises to

-126

short real

and

exponent

of

true result <

-126

(true), round significand to 24 bits, store true 0

(true). if denormalized rounded significand =

0;

else,

store denormal (biased exponent =

0).

(FST,

FSTP instructions only): destination is

Denormalize until exponent rises to

-1022

long

real

and

exponent of true result <

-1022

(true), round significand to 53 bits, store true 0

(true). if rounded denormalized significand =

0;

else,

store denormal (biased exponent

=

0).

Precision

True rounding error occurs. No special action.

Masked response to overflow exception earlier

No

special action.

in

instruction.

Note that when exceptions are masked, the

NPX

may detect multiple exceptions in a single instruction,

because it continues executing the instruction after performing its masked response. For example, the

80287 could detect a denormalized operand, perform its masked response to this exception, and then

detect an underflow.

1-36