THE

80286

INSTRUCTION SET

X

CHG

- Exchange Memory/Register with Register

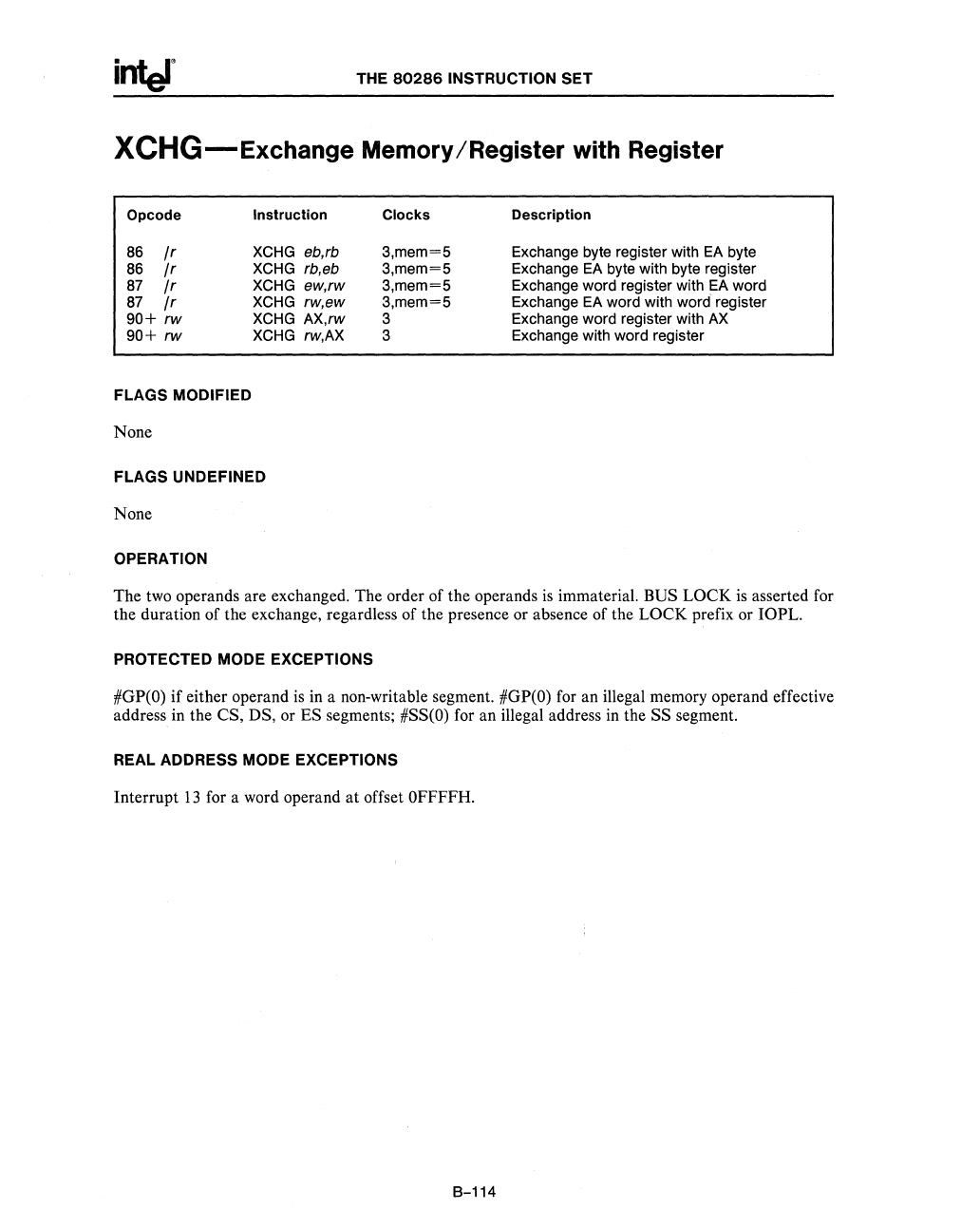

Opcode

Instruction Clocks Description

86

Ir

XCHG

eb,rb

3,mem=5

Exchange byte register with

EA

byte

86

Ir

XCHG

rb,eb

3,mem=5

Exchange

EA

byte with byte register

87

Ir

XCHG

eW,rw

3,mem=5

Exchange word register with

EA

word

87

Ir

XCHG

rW,ew

3,mem=5

Exchange

EA

word with word register

90+

rw

XCHG

AX,rw 3

Exchange word register with

AX

90+

rw

XCHG

rW,AX

3

Exchange with word register

FLAGS MODIFIED

None

FLAGS UNDEFINED

None

OPERATION

The

two operands are exchanged.

The

order

of

the operands

is

immaterial. BUS

LOCK

is

asserted for

the duration

of

the exchange, regardless

of

the presence or absence of the

LOCK

prefix or IOPL.

PROTECTED MODE EXCEPTIONS

#GP(O)

if

either operand

is

in a non-writable segment. #GP(O) for an illegal memory operand effective

address in the

CS,

DS, or

ES

segments; #SS(O) for an illegal address

in

the

SS

segment.

REAL ADDRESS MODE EXCEPTIONS

Interrupt

13

for a word operand

at

offset OFFFFH.

8-114