80286

BASE

ARCHITECTURE

MEMORY

ADDRESS

SPACE

110

DEVICE

1

INTERNAL

REGISTER

1-------11--

= = = = =

~

....

I

___

.....

110

DEVICE

2

INTERNAL

REGISTER

1-------1

= = = = = =

~

....

I

___

.....

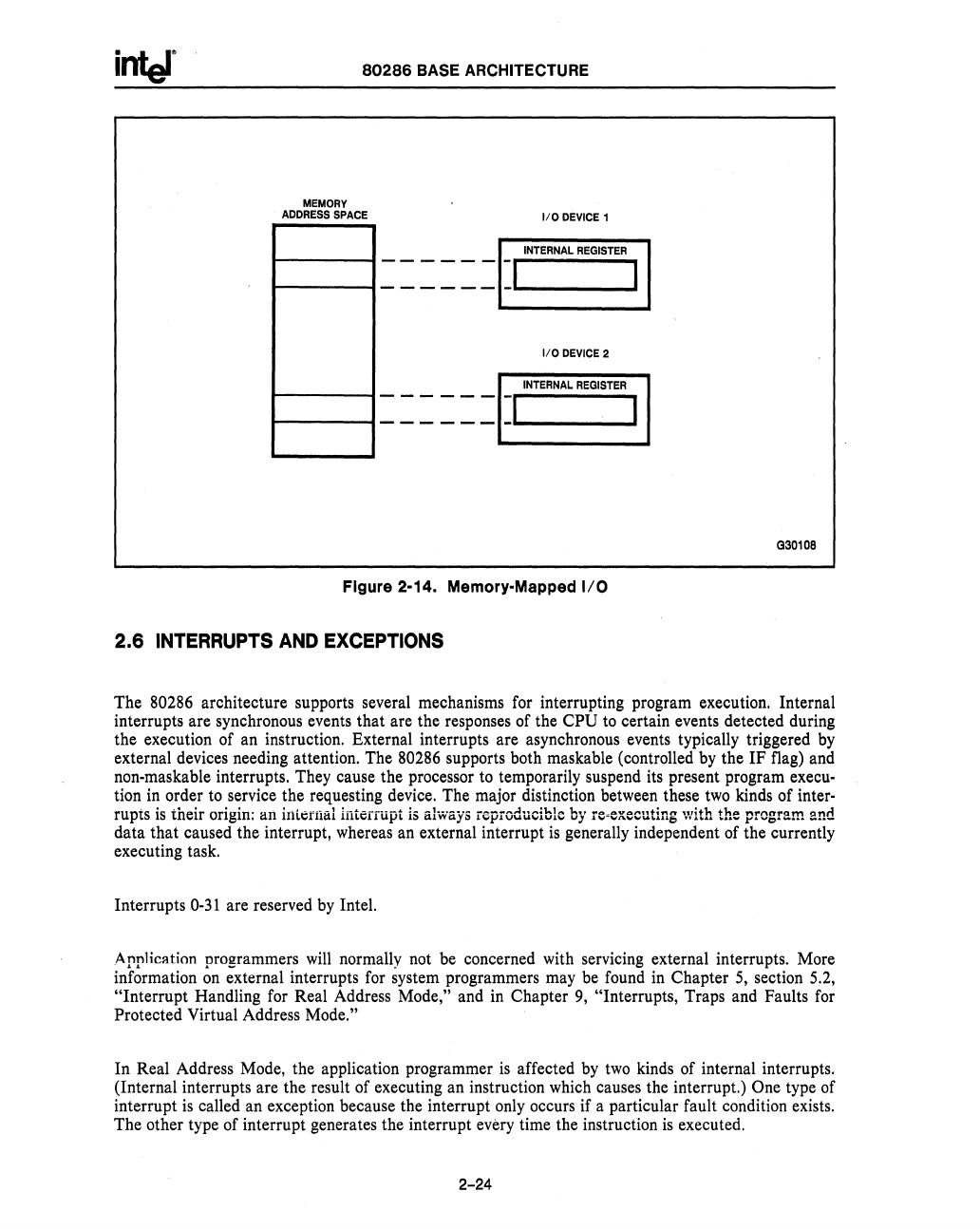

Figure 2-14. Memory-Mapped

1/0

2.6

INTERRUPTS

AND

EXCEPTIONS

G30108

The 80286 architecture supports several mechanisms for interrupting program execution. Internal

interrupts are synchronous events that are the responses of the

CPU

to

certain events detected during

the execution of an instruction. External interrupts are asynchronous events typically triggered

by

external devices needing attention. The 80286 supports both maskable (controlled

by

the IF flag) and

non-maskable interrupts. They cause the processor to temporarily suspend its present program

execu-

tion

in

order

to

service the requesting device. The major distinction between these

two

kinds of inter-

rupts

is

their

origin;

art

internal

interrupt

is

always

repioducible

by

re-executing

\vith

the

program

and

data that caused the interrupt, whereas

an

external interrupt

is

generally independent of the currently

executing task.

Interrupts

0-31

are reserved

by

Intel.

Application programmers

will

normally not be concerned with servicing external interrupts. More

information

on

external interrupts for system programmers may be found in Chapter

5,

section 5.2,

"Interrupt Handling for Real Address Mode," and

in

Chapter

9,

"Interrupts, Traps and Faults

for

Protected Virtual Address Mode."

In Real Address Mode, the application programmer

is

affected by

two

kinds of internal interrupts.

(Internal interrupts are the result of executing an instruction which causes the interrupt.)

One type of

interrupt

is

called an exception because the interrupt only occurs if a particular fault condition exists.

The other type of interrupt generates the interrupt

every time the instruction

is

executed.

2-24