80286

BASE

ARCHITECTURE

Beyond their code and stack requirements, most programs must also fetch and store data

in

memory.

The

DS and ES registers

allow

the specification of

two

data segments, each addressable

by

the currently

executing program. Accessibility to

two

separate data areas supports differentiation and access require-

ments like local procedure data and global process data.

An

operand within a data segment

is

addressed

by specifying its offset either directly in an instruction or indirectly via index and/or base registers

(described

in

the next subsection).

Depending

on

the data structure (e.g., the

way

data

is

parceled into

one

or more segments), a program

may require access to multiple data segments. To access additional segments, the

DS and ES registers

can be loaded under program control during the course of a program's execution. This simply requires

loading the appropriate data pointer prior to accessing the data.

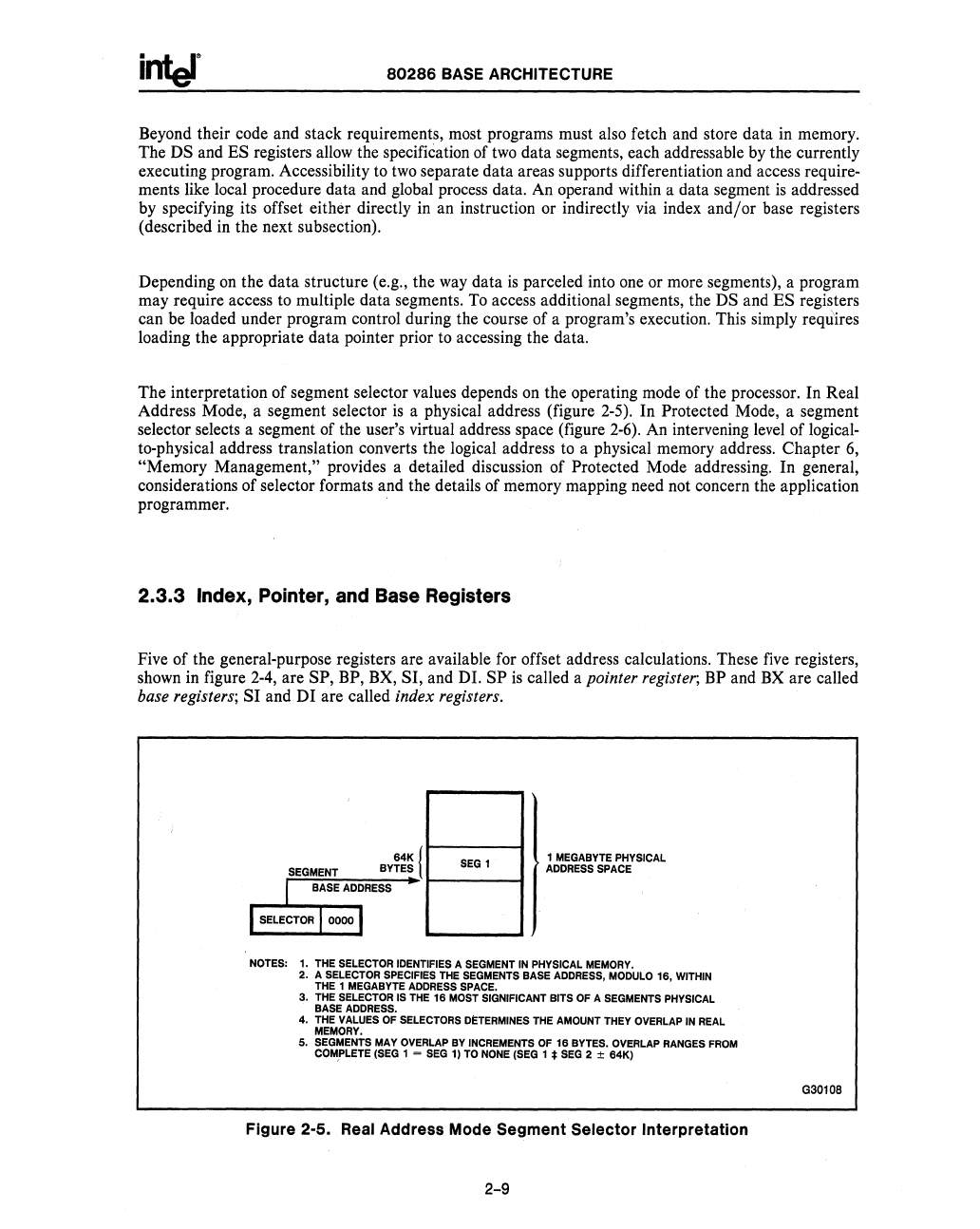

The interpretation of segment selector values depends

on

the operating mode of the processor. In Real

Address Mode, a segment selector

is

a physical address (figure 2-5). In Protected Mode, a segment

selector selects a segment of the user's virtual address space (figure

2-6).

An

intervening

level

of logical-

to-physical address translation converts the logical address

to

a physical memory address. Chapter 6,

"Memory Management," provides a detailed discussion of Protected Mode addressing. In general,

considerations of selector formats and the details of memory mapping need not concern the application

programmer.

2.3.3

Index, Pointer,

and

Base Registers

Five of the general-purpose registers are available for offset address calculations. These

five

registers,

shown

in

figure

2-4,

are SP, BP, BX, SI, and

DL

SP

is

called a pointer register; BP and

BX

are called

base registers;

SI

and DI are called index registers.

SEGMENT

64K

{

BYTES

I

BASE ADDRESS

SEG

1

1 MEGABYTE PHYSICAL

ADDRESS SPACE

I SELECTOR I

0000

I

NOTES: 1. THE SELECTOR IDENTIFIES A SEGMENT

IN

PHYSICAL MEMORY.

2. A SELECTOR SPECIFIES THE SEGMENTS BASE ADDRESS, MODULO 16, WITHIN

THE 1 MEGABYTE ADDRESS SPACE.

3. THE SELECTOR IS THE

16

MOST SIGNIFICANT BITS

OF

A SEGMENTS PHYSICAL

BASE ADDRESS.

4. THE VALUES

OF

SELECTORS DETERMINES THE AMOUNT THEY OVERLAP

IN

REAL

MEMORY.

5. SEGMENTS MAY OVERLAP BY INCREMENTS

OF

16

BYTES. OVERLAP RANGES FROM

COMPLETE (SEG 1

~

SEG

1) TO NONE (SEG 1 *

SEG

2 ±

64K)

Figure 2-5. Real Address Mode Segment Selector Interpretation

2-9

G3010a