PROGRAMMING NUMERIC APPLICATIONS

INCORRECT ERROR SYNCHRONIZATION

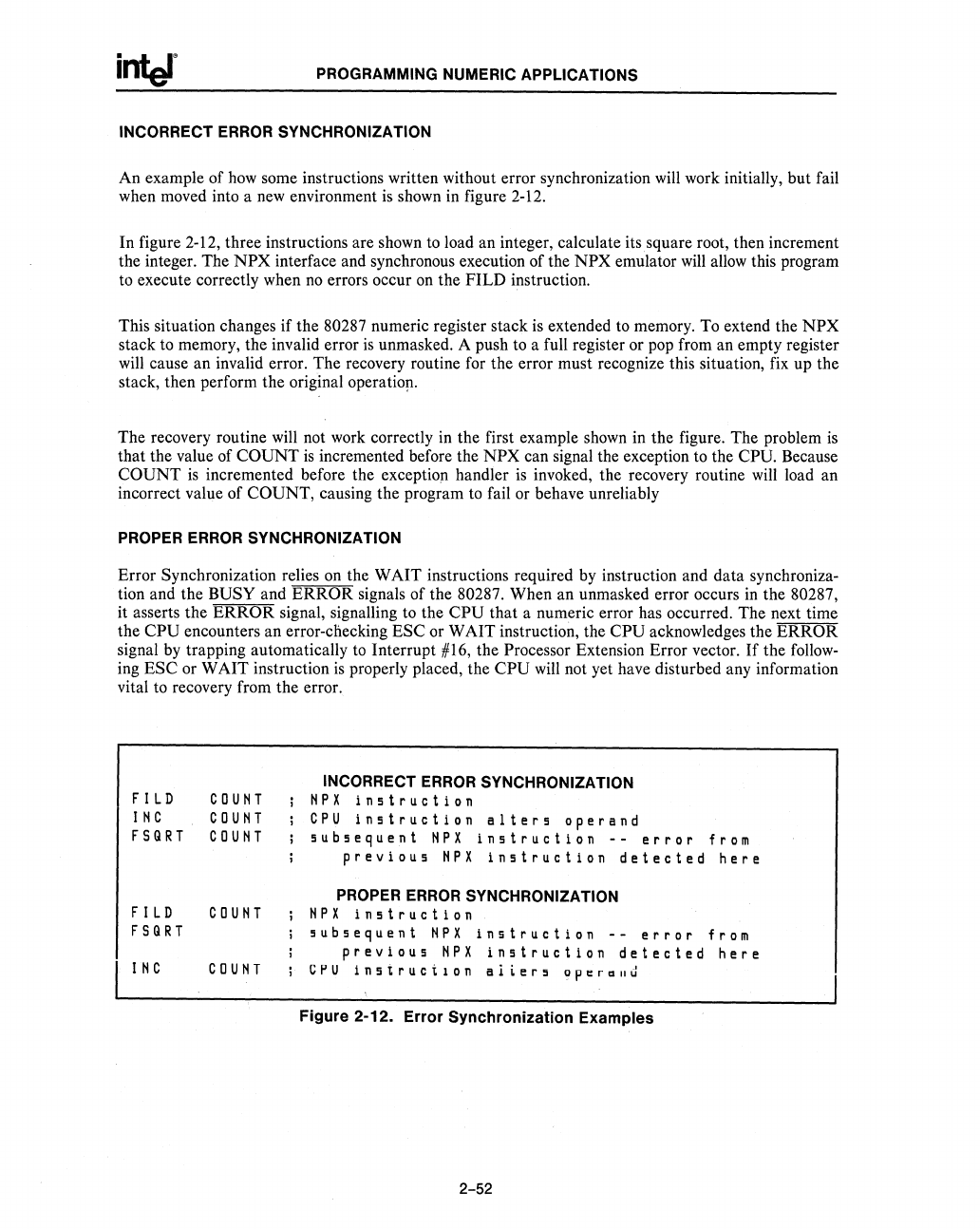

An example of

how

some instructions written without error synchronization

will

work initially, but fail

when moved into a new environment

is

shown

in

figure

2-12.

In figure 2-12, three instructions are shown

to

load an integer, calculate its square root, then increment

the integer. The

NPX

interface and synchronous execution of the NPX emulator

will

allow

this program

to execute correctly when

no

errors occur

on

the FILD instruction.

This situation changes if the

80287 numeric register stack

is

extended to memory. To extend the

NPX

stack to memory, the invalid error

is

unmasked. A push to a full register or pop from an empty register

will

cause an invalid error. The recovery routine for the error must recognize this situation, fix up the

stack, then perform the original

operatioll.

The recovery routine

will

not work correctly

in

the first example shown in the figure. The problem

is

that the value of COUNT

is

incremented before the NPX can signal the exception to the CPU. Because

COUNT

is

incremented before the exception handler

is

invoked, the recovery routine

will

load an

incorrect value of

COUNT, causing the program to fail or behave unreliably

PROPER ERROR SYNCHRONIZATION

Error Synchronization relies

on

the WAIT instructions required

by

instruction and data synchroniza-

tion and the

BUSY and

ERROR

signals of the 80287. When an unmasked error occurs

in

the 80287,

it asserts the

ERROR

signal, signalling to the

CPU

that a numeric error has occurred. The next time

the

CPU encounters an error-cliecking ESC or WAIT instruction, the CPU acknowledges the

ERROR

signal

by

trapping automatically

to

Interrupt #16, the Processor Extension Error vector.

If

the

follow-

ing ESC or WAIT instruction

is

properly placed, the CPU

will

not yet have disturbed any information

vital to recovery from the error.

F I L D

1M

C

FSGRT

F I L D

FSGRT

INC

COUNT

COUNT

COUNT

COUNT

COUNT

INCORRECT ERROR SYNCHRONIZATION

NPX

instruction

CPU

instruction

alters

operand

subsequent

NPX

instruction

--

error

from

previous

NPX

instruction

detected

here

PROPER ERROR SYNCHRONIZATION

NPX

instruction

subsequent

NPX

instruction

--

error

from

previous

NPX

instruction

detected

here

CPU

instruction

aiiers

op"rollu

Figure 2-12. Error Synchronization Examples

2-52