112

CHAPTER 5 CPU ARCHITECTURE

5.2.2 General registers

A general register is mapped at particular addresses (FEE0H to FEFFH) of the data memory. It consists of 4 banks,

each bank consisting of eight 8-bit registers (X, A, C, B, E, D, L and H).

Each register can also be used as an 8-bit register. Two 8-bit registers can be used in pairs as a 16-bit register

(AX, BC, DE and HL).

They can be described in terms of function names (X, A, C, B, E, D, L, H, AX, BC, DE and HL) and absolute names

(R0 to R7 and RP0 to RP3).

Register banks to be used for instruction execution are set with the CPU control instruction (SEL RBn). Because

of the 4-register bank configuration, an efficient program can be created by switching between a register for normal

processing and a register for interruption for each bank.

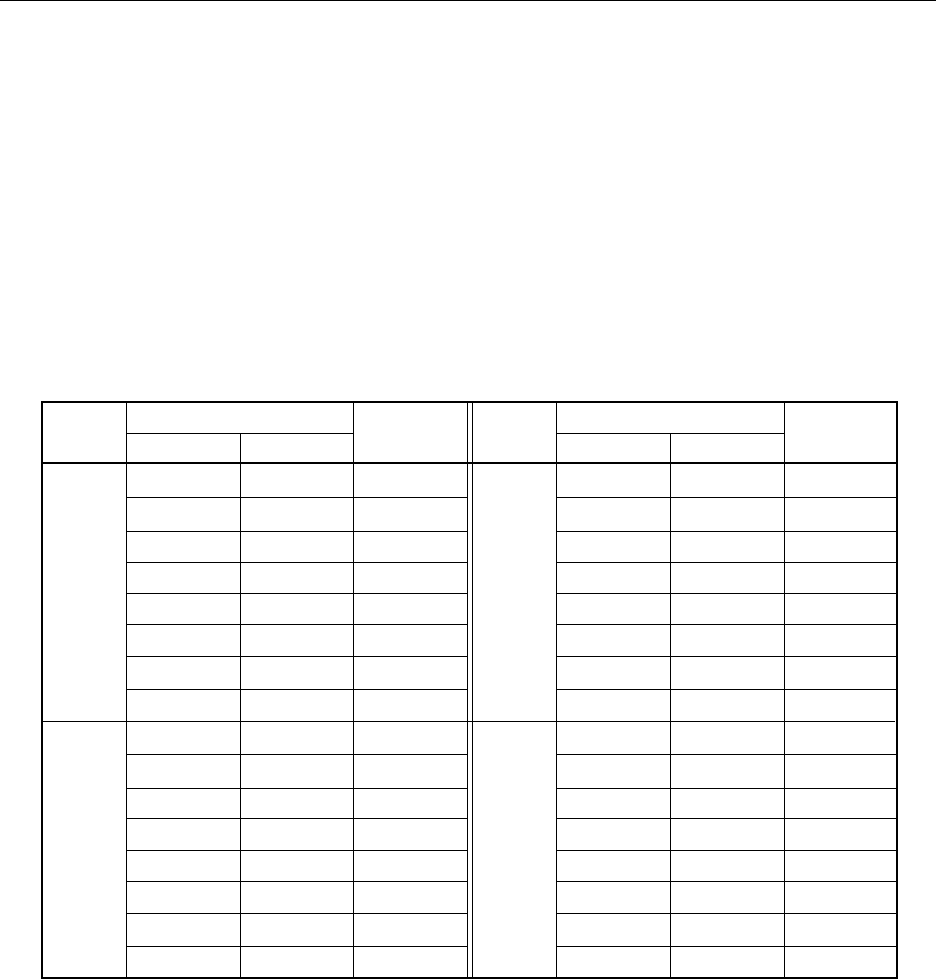

Table 5-5. Correspondent Table of Absolute Addresses in the General Registers

Bank Register Absolute Bank Register Absolute

Functional Name Absolute Name

Address

Functional Name Absolute Name

Address

BANK0 H R7 FEFFH BANK2 H R7 FEEFH

L R6 FEFEH L R6 FEEEH

D R5 FEFDH D R5 FEEDH

E R4 FEFCH E R4 FEECH

B R3 FEFBH B R3 FEEBH

C R2 FEFAH C R2 FEEAH

A R1 FEF9H A R1 FEE9H

X R0 FEF8H X R0 FEE8H

BANK1 H R7 FEF7H BANK3 H R7 FEE7H

L R6 FEF6H L R6 FEE6H

D R5 FEF5H D R5 FEE5H

E R4 FEF4H E R4 FEE4H

B R3 FEF3H B R3 FEE3H

C R2 FEF2H C R2 FEE2H

A R1 FEF1H A R1 FEE1H

X R0 FEF0H X R0 FEE0H