Rev.1.02 Jul 01, 2005 page 163 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

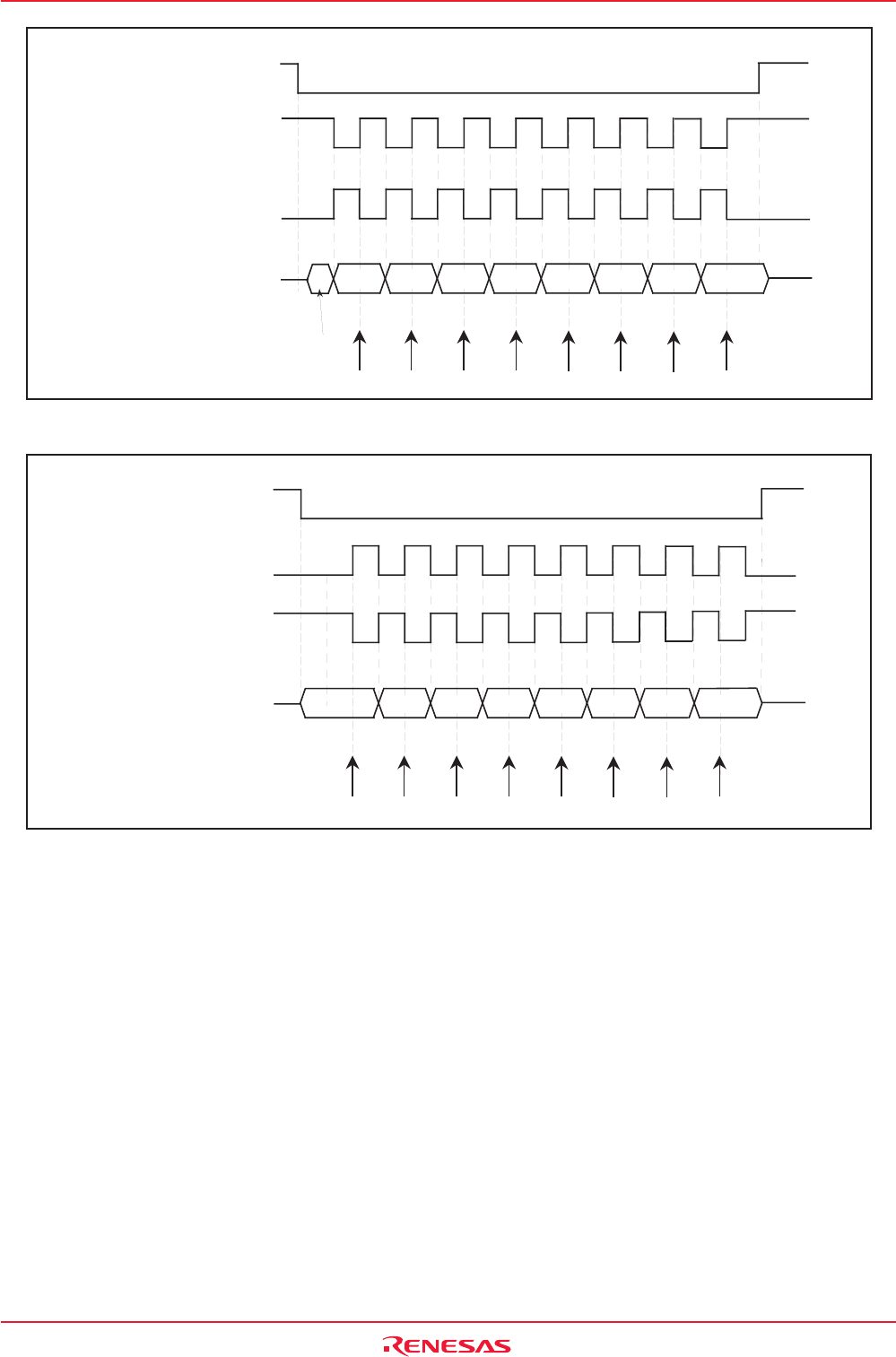

Figure 14.29 Transmission and Reception Timing (CKPH = 0) in Slave Mode (External Clock)

Figure 14.30 Transmission and Reception Timing (CKPH = 1) in Slave Mode (External Clock)

D0 D1 D2 D3 D4 D6 D7D5

Indeterminate

Slave control input

Clock input

(CKPOL= 0, CKPH = 0)

Clock input

(CKPOL = 1, CKPH = 0)

Data output timing

Data input timing

"H"

"L"

"H"

"L"

"H"

"L"

"H"

"L"

D0 D1 D2 D3 D6 D7D4 D5

Slave control input

Clock input

(CKPOL = 0, CKPH = 1)

Clock input

(CKPOL = 1, CKPH = 1)

Data output timing

Data input timing

"H"

"L"

"H"

"L"

"H"

"L"

"H"

"L"