Rev.1.02 Jul 01, 2005 page 59 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 9. Interrupt

Under development

This document is under development and its contents are subject to change.

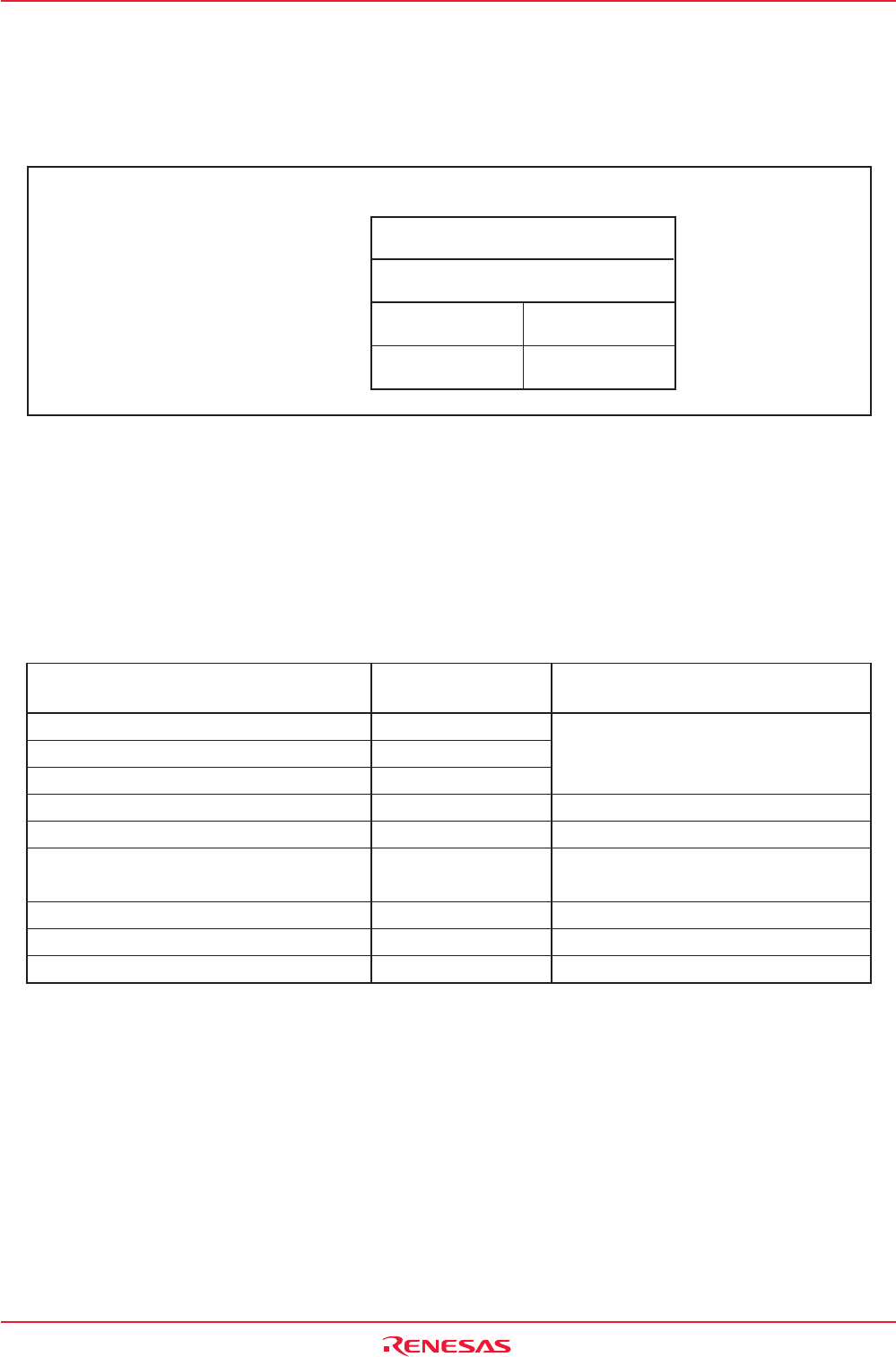

Figure 9.2 Interrupt Vector

9.4.1 Fixed Vector Tables

The fixed vector tables are allocated to the addresses from FFFDCh to FFFFFh. Table 9.1 lists the fixed

vector tables. In the flash memory version of microcomputer, the vector addresses (H) of fixed vectors are

used by the ID code check function. For details, refer to 20.2 Functions to Prevent Flash Memory from

Rewriting.

Table 9.1 Fixed Vector Tables

9.4 Interrupts and Interrupt Vector

One interrupt vector consists of 4 bytes. Set the start address of each interrupt routine in the respective

interrupt vectors. When an interrupt request is accepted, the CPU branches to the address set in the

corresponding interrupt vector. Figure 9.2 shows the interrupt vector.

Low-order address

Middle-order address

Vector address (L)

Vector address (H)

0 0 0 0

0 0 0 0 0 0 0 0

MSB LSB

High-order address

Interrupt Source

Vector table Addresses

Reference

Address (L) to Address (H)

Undefined Instruction (UND instruction) FFFDChto FFFDFh M16C/60, M16C/20 Series Software

Overflow (INTO instruction) FFFE0h to FFFE3h Manual

BRK Instruction

(2)

FFFE4h to FFFE7h

Address Match FFFE8h to FFFEBh 9.10 Address Match Interrupt

Single Step

(1)

FFFECh to FFFEFh

Oscillation Stop and Re-oscillation Detection, FFFF0h to FFFF3h 7. Clock Generating Circuit

Watchdog Timer 10. Watchdog Timer

________

DBC

(1)

FFFF4h to FFFF7h

_______

NMI FFFF8h to FFFFBh

_______

9.7 NMI Interrupt

Reset FFFFCh to FFFFFh 5. Reset

NOTES:

1. Do not normally use this interrupt because it is provided exclusively for use by development support

tools.

2. If the contents of address FFFE7h is FFh, program execution starts from the address shown by the

vector in the relocatable vector table.

9.4.2 Relocatable Vector Tables

The 256 bytes beginning with the start address set in the INTB register comprise a relocatable vector

table area. Table 9.2 lists the relocatable vector tables. Setting an even address in the INTB register results

in the interrupt sequence being executed faster than in the case of odd addresses.