Rev.1.02 Jul 01, 2005 page 178 of 314

REJ09B0126-0102

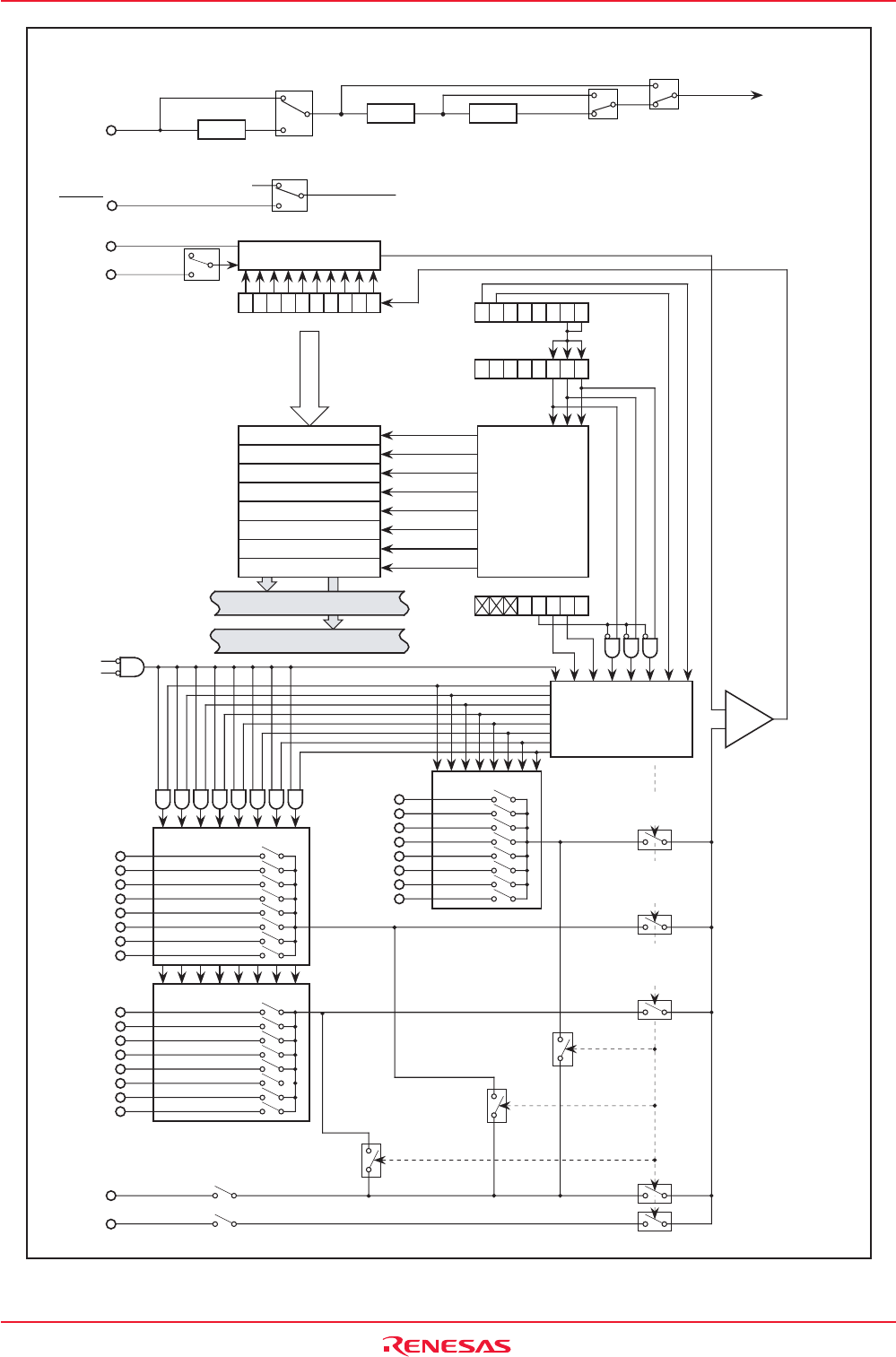

M16C/6N Group (M16C/6NL, M16C/6NN) 15. A/D Converter

Under development

This document is under development and its contents are subject to change.

Figure 15.1 A/D Converter Block Diagram

ANEX0

ANEX1

OPA0=1

OPA1=1

ADGSEL1 to ADGSEL0=00b

OPA1 to OPA0=11b

=000b

=001b

=010b

=011b

=100b

=101b

=110b

=111b

VREF

VIN

CH2 to CH0

PM00

PM01

Decoder

for channel

selection

Data bus low-order

VCUT

1

0

Data bus high-order

OPA1=1

Port P10 group

Port P0 group

ADGSEL1 to ADGSEL0=00b

OPA1 to OPA0=00b

OPA1 to OPA0

=01b

CKS0

0

1

0

1

0

1

1/3

CKS2

1/21/2

φAD

A/D conversion rate selection

Resistor ladder

Successive conversion register

Comparator

Decoder

for A/D register

Port P2 group

TRG

0

1

A/D trigger

Software trigger

=000b

=001b

=010b

=011b

=100b

=101b

=110b

=111b

=000b

=001b

=010b

=011b

=100b

=101b

=110b

=111b

CH2 to CH0

CH2 to CH0

AD0 register

AD1 register

AD2 register

AD3 register

AD4 register

AD5 register

AD6 register

AD7 register

ADCON0 register

ADCON1 register

ADCON2 register

VREF

AVSS

fAD

ADTRG

PM01 to PM00=00b

ADGSEL1 to ADGSEL0=10b

OPA1 to OPA0=00b

PM01 to PM00=00b

ADGSEL1 to ADGSEL0=10b

OPA1 to OPA0=00b

AN0_0

AN0_1

AN0_2

AN0_3

AN0_4

AN0_5

AN0_6

AN0_7

AN2_0

AN2_1

AN2_2

AN2_3

AN2_4

AN2_5

AN2_6

AN2_7

AN0

AN0

AN0

AN0

AN0

AN0

AN0

AN0

PM01 to PM00=00b

ADGSEL1 to ADGSEL0=10b

OPA1 to OPA0=11b

PM01 to PM00=00b

ADGSEL1 to ADGSEL0=11b

OPA1 to OPA0=11b

CKS1