Rev.1.02 Jul 01, 2005 page 12 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 3. Memory

Under development

This document is under development and its contents are subject to change.

3. Memory

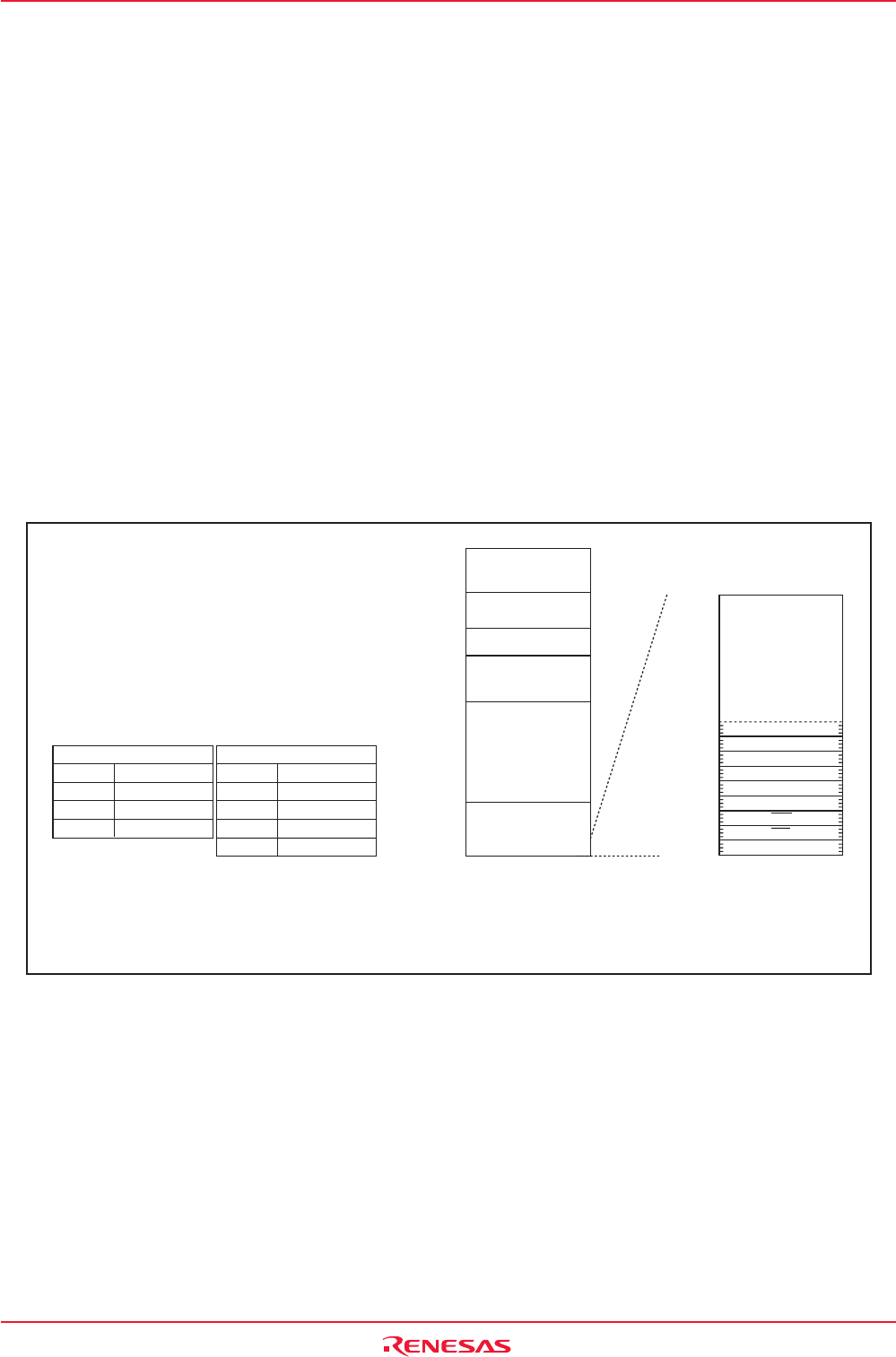

Figure 3.1 shows a memory map of the M16C/6N Group (M16C/6NL, M16C/6NN). The address space

extends the 1 Mbyte from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a

512-Kbyte internal ROM is allocated to the addresses from 80000h to FFFFFh.

As for the flash memory version, 4-Kbyte space (block A) exists in 0F000h to 0FFFFh. 4-Kbyte space is

mainly for storing data. In addition to storing data, 4-Kbyte space also can store programs.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the

start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a

31-Kbyte internal RAM is allocated to the addresses from 00400h to 07FFFh. In addition to storing data, the

internal RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SFR is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are

located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be

used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by

the JMPS or JSRS instruction. For details, refer to M16C/60 and M16C/20 Series Software Manual.

Figure 3.1 Memory Map

00000h

YYYYY

h

FFFFFh

00400h

0FFFFh

10000h

0F000h

XXXXX

h

Internal ROM

(data area)

(1)

Internal ROM

(program area)

(3)

SFR

Internal RAM

Reserved area

FFE00h

FFFDCh

FFFFFh

NOTES:

1. As for the flash memory version, 4-Kbyte space (block A) exists.

2. Shown here is a memory map for the case where the PM13 bit in the PM1 register is "1".

If the PM13 bit is set to "0", 15 Kbytes of the internal RAM and 192 Kbytes of the internal ROM can be used.

3. When using the masked ROM version, write nothing to internal ROM area.

Undefined instruction

Overflow

BRK instruction

Address match

Single step

Oscillation stop and re-oscillation

detection / watchdog timer

Reset

Special page

vector table

DBC

NMI

Address XXXXX

h

Capacity

Internal RAM

20 Kbytes

31 Kbytes

053FF

h

16 Kbytes 043FF

h

07FFF

h

Address YYYYY

h

Capacity

Internal ROM

(1)

384 Kbytes A0000

h

256 Kbytes C0000

h

192 Kbytes D0000

h

512 Kbytes 80000

h

Reserved area