Rev.1.02 Jul 01, 2005 page 75 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 9. Interrupt

Under development

This document is under development and its contents are subject to change.

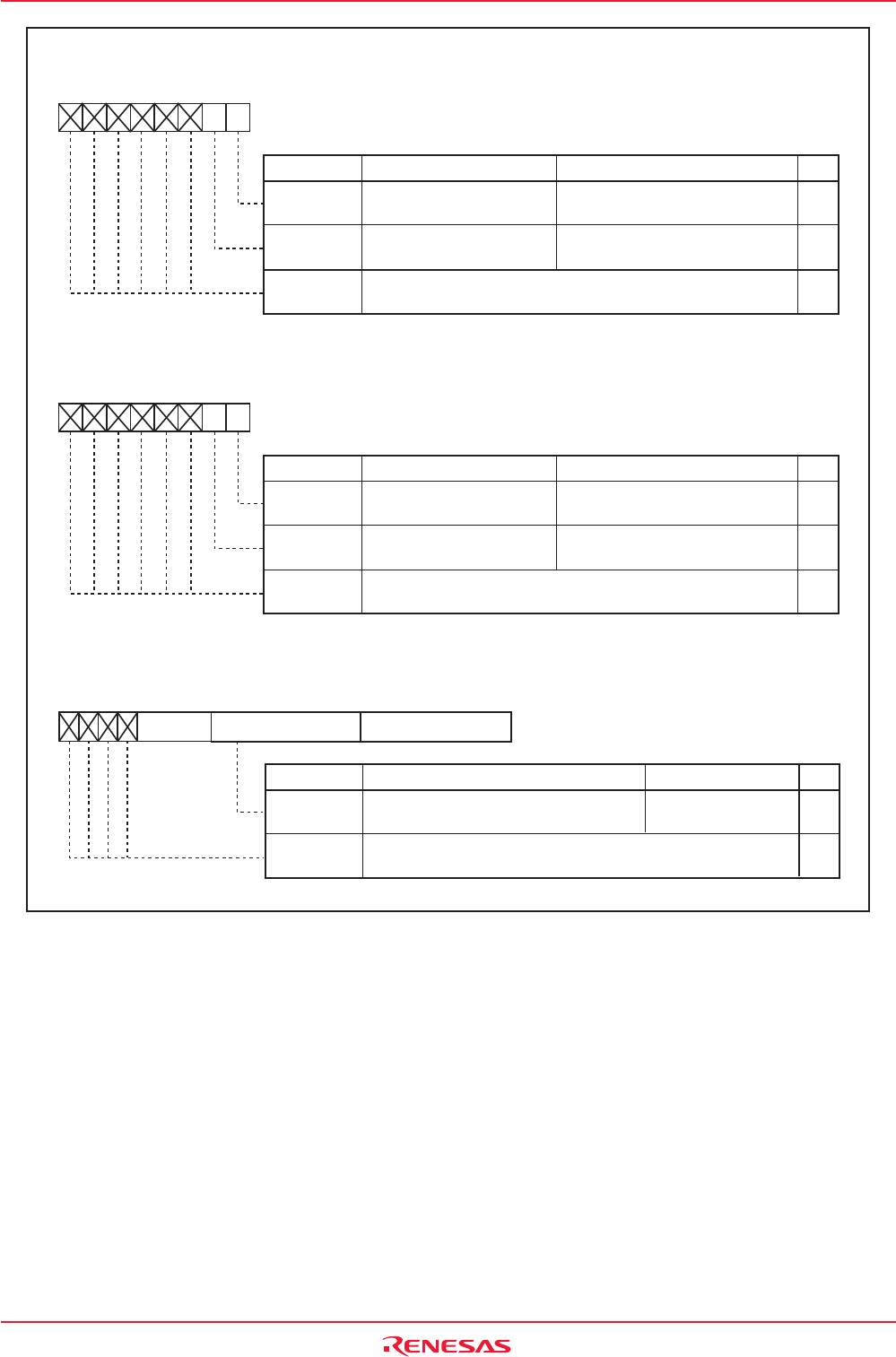

Figure 9.16 AIER Register, AIER2 Register and RMAD0 to RMAD3 Registers

RW

-

Address Match Interrupt Enable Register

Address Match Interrupt 0

Enable Bit

Address Match Interrupt 1

Enable Bit

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

Symbol Address After Reset

AIER 0009h XXXXXX00b

AIER0

AIER1

-

(b7-b2)

RW

Bit Name Function

Bit Symbol

RW

Nothing is assigned. When write, set to "0".

When read, their contents are indeterminate.

b7 b6 b5 b4 b3 b2 b1 b0

RW

-

Address Match Interrupt Enable Register 2

Address Match Interrupt 2

Enable Bit

Address Match Interrupt 3

Enable Bit

0 : Interrupt disabled

1 : Interrupt enabled

0 : Interrupt disabled

1 : Interrupt enabled

Symbol Address After Reset

AIER2 01BBh XXXXXX00b

AIER20

AIER21

-

(b7-b2)

RW

Bit Name Function

Bit Symbol

RW

Nothing is assigned. When write, set to "0".

When read, their contents are indeterminate.

b7 b6 b5 b4 b3 b2 b1 b0

RW

-

-

(b19-b0)

-

(b23-b20)

Bit Symbol

AddressSymbol After Reset

0012h to 0010h

0016h to 0014h

01BAh to 01B8h

01BEh to 01BCh

RMAD0

RMAD1

RMAD2

RMAD3

X00000h

X00000h

X00000h

X00000h

Function

Setting Range

RW

Address setting register for address

match interrupt

Nothing is assigned. When write, set to "0".

When read, their contents are indeterminate.

Address Match Interrupt Register i (i = 0 to 3)

00000h to FFFFFh

b0 b7 b0b3

(b19) (b16)

b7 b0

(b15) (b8)

b7

(b23)