Rev.1.02 Jul 01, 2005 page 41 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 7. Clock Generating Circuit

Under development

This document is under development and its contents are subject to change.

7.1.3 On-chip Oscillator Clock

This clock, approximately 1 MHz, is supplied by a on-chip oscillator. This clock is used as the clock

source for the CPU and peripheral function clocks. In addition, if the PM22 bit in the PM2 register is “1”

(on-chip oscillator clock for the watchdog timer count source), this clock is used as the count source for

the watchdog timer (refer to 10.1 Count Source Protective Mode).

After reset, the on-chip oscillator is turned off. It is turned on by setting the CM21 bit in the CM2 register

to “1” (on-chip oscillator clock), and is used as the clock source for the CPU and peripheral function

clocks, in place of the main clock. If the main clock stops oscillating when the CM20 bit in the CM2 register

is “1” (oscillation stop, re-oscillation detection function enabled) and the CM27 bit is “1” (oscillation stop,

re-oscillation detection interrupt), the on-chip oscillator automatically starts operating, supplying the nec-

essary clock for the microcomputer.

7.1.4 PLL Clock

The PLL clock is generated by a PLL frequency synthesizer. This clock is used as the clock source for the

CPU and peripheral function clocks. After reset, the PLL clock is turned off. The PLL frequency synthe-

sizer is activated by setting the PLC07 bit to “1” (PLL operation). When the PLL clock is used as the clock

source for the CPU clock, wait a fixed period of tsu(PLL) for the PLL clock to be stable, and then set the

CM11 bit in the CM1 register to “1”.

Before entering wait mode or stop mode, be sure to set the CM11 bit to “0” (CPU clock source is the main

clock). Furthermore, before entering stop mode, be sure to set the PLC07 bit in the PLC0 register to “0”

(PLL stops). Figure 7.11 shows the procedure for using the PLL clock as the clock source for the CPU.

The PLL clock frequency is determined by the equation below.

PLL clock frequency = f(XIN) ✕ (multiplying factor set by the PLC02 to PLC00 bits in the PLC0 register)

(However, PLL clock frequency = 16 MHz, 20 MHz or 24 MHz)

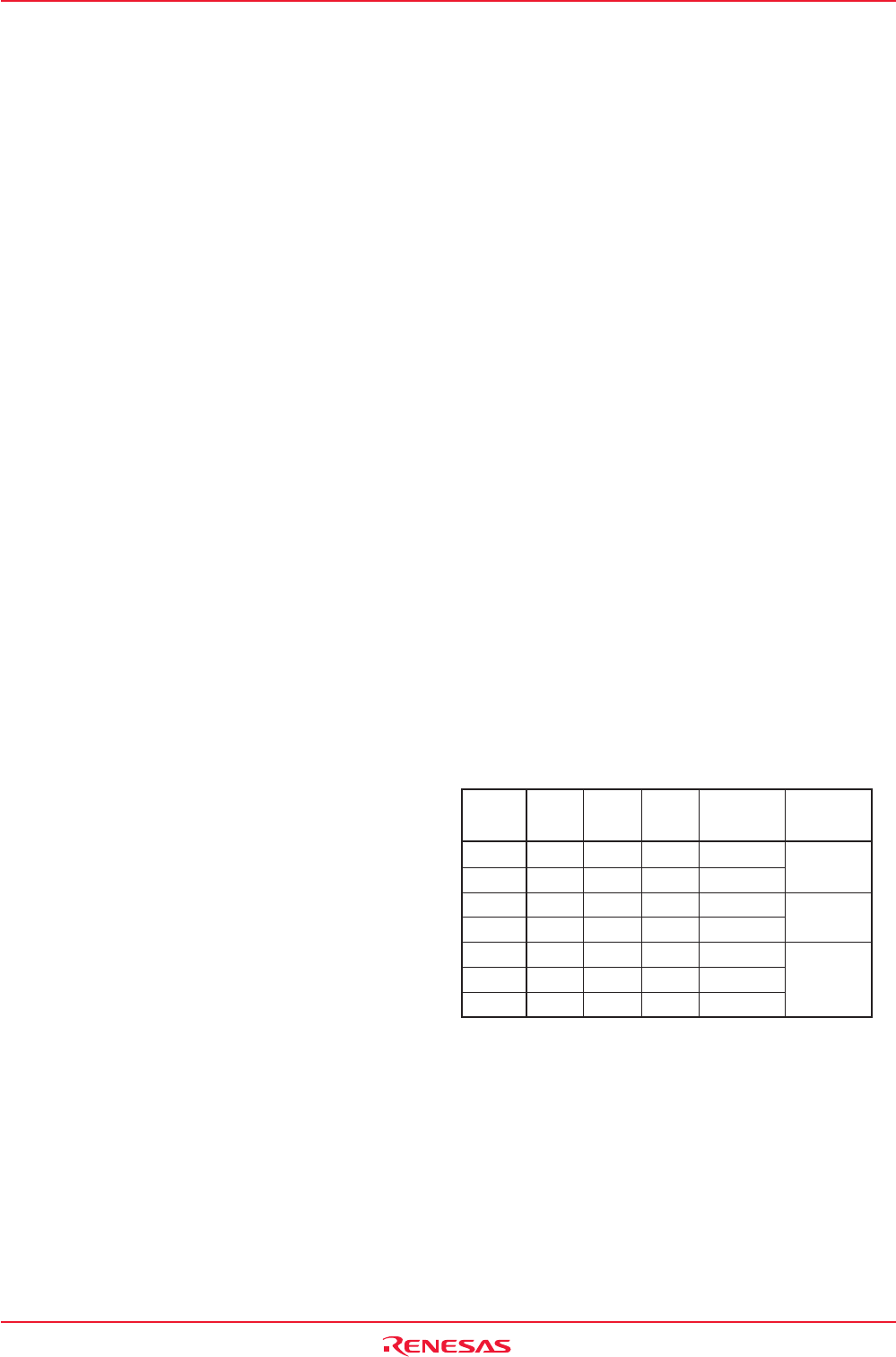

The PLC02 to PLC00 bits can be set only once after reset. Table 7.2 shows the example for setting PLL

clock frequencies.

Table 7.2 Example for Setting PLL Clock Frequencies

XIN

(MHz)

8

4

10

5

12

6

4

Multiply

Factor

PLL Clock

(MHz)

(1)

PLC01 PLC00

0

0

0

0

0

0

0

0

1

0

1

0

1

1

1

0

1

0

1

0

1

2

4

2

4

2

4

6

16

20

24

NOTE:

1. PLL clock frequency = 16 MHz , 20 MHz or 24 MHz

PLC02