Rev.1.02 Jul 01, 2005 page 71 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 9. Interrupt

Under development

This document is under development and its contents are subject to change.

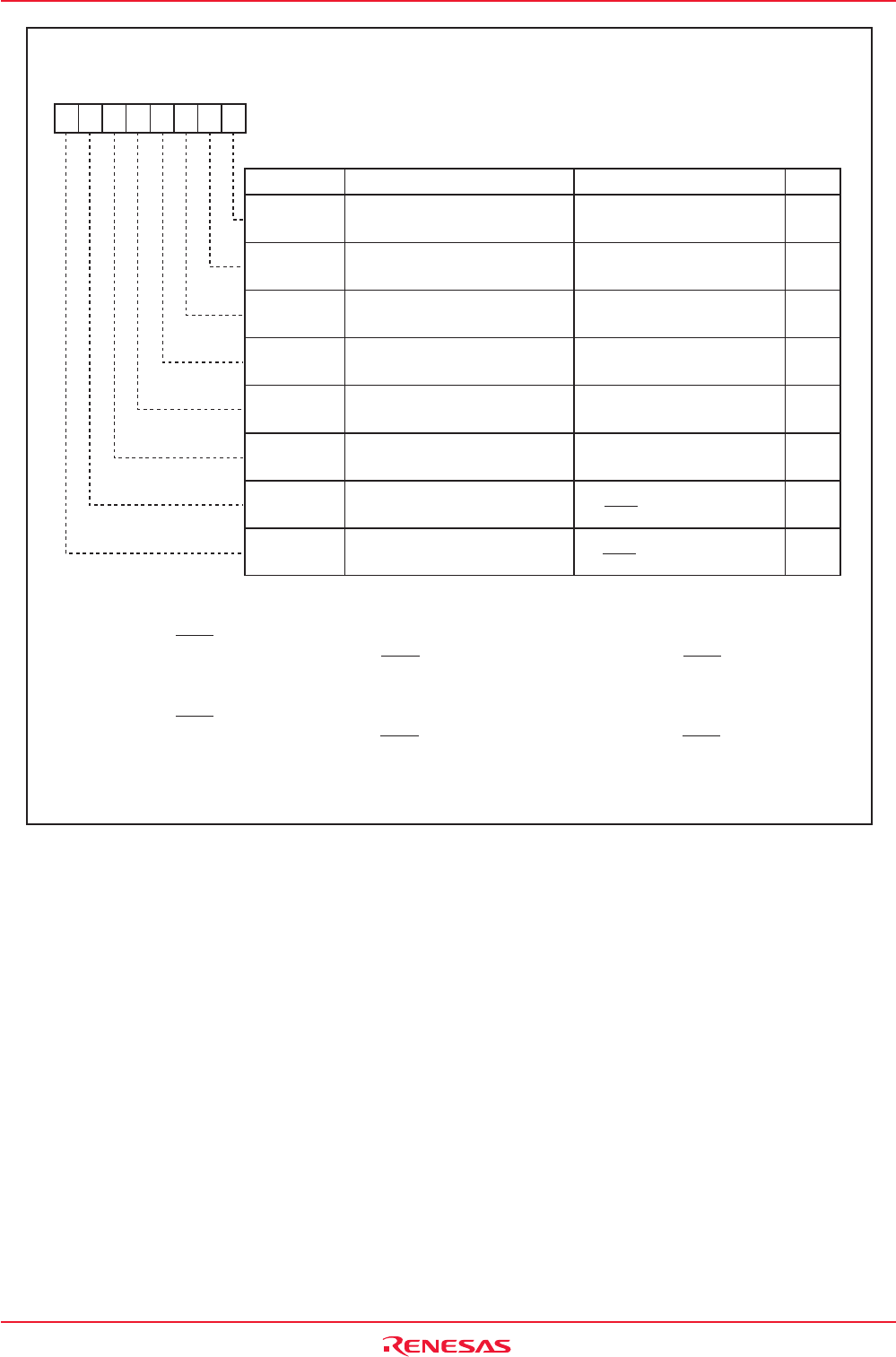

Figure 9.12 IFSR1 Register

Interrupt Request Cause Select Register 1

RW

Symbol Address After Reset

IFSR1 01DFh 00h

RW

RW

RW

RW

RW

RW

RW

RW

b7 b6 b5 b4 b3 b2 b1 b0

0 : SI/O3

(3)

1 : INT4

0 : SI/O4

(5)

1 : INT5

0 : One edge

1 : Both edges

(1)

0 : One edge

1 : Both edges

(1)

0 : One edge

1 : Both edges

(1)

0 : One edge

1 : Both edges

(1)

0 : One edge

1 : Both edges

(1)

0 : One edge

1 : Both edges

(1)

IFSR10

Interrupt Request Cause

Select Bit

(2)

Interrupt Request Cause

Select Bit

(4)

IFSR11

IFSR12

IFSR13

IFSR14

IFSR15

IFSR16

IFSR17

Bit Name Function

Bit Symbol

INT0 Interrupt Polarity

Switching Bit

INT1 Interrupt Polarity

Switching Bit

INT2 Interrupt Polarity

Switching Bit

INT3 Interrupt Polarity

Switching Bit

INT4 Interrupt Polarity

Switching Bit

INT5 Interrupt Polarity

Switching Bit

NOTES:

1.When setting this bit to "1" (both edges), make sure the POL bit in the INT0IC to INT5IC register is set

to "0" (falling edge).

2.SI/O3 and INT4 share the vector and interrupt control register. When using SI/O3 interrupt, set the

IFSR16 bit to "0" (SI/O3). When using INT4 interrupt, set the IFSR16 bit to "1" (INT4).

3.When setting this bit to "0" (SI/O3), make sure the IFSR00 bit in the IFSR0 register is set to "1" (SI/O3)

simultaneously. And, make sure the POL bit in the S3IC register is set to "0" (falling edge).

4.SI/O4 and INT5 share the vector and interrupt control register. When using SI/O4 interrupt, set the

IFSR17 bit to "0" (SI/O4). When using INT5 interrupt, set the IFSR17 bit to "1" (INT5).

5.When setting this bit to "0" (SI/O4), make sure the IFSR03 bit in the IFSR0 register is set to "1" (SI/O4)

simultaneously. And, make sure the POL bit in the S4IC register is set to "0" (falling edge).