4.57ControlStatusRegisterforEndpoint0inPeripheralMode(PERI_CSR0)

Registers

www.ti.com

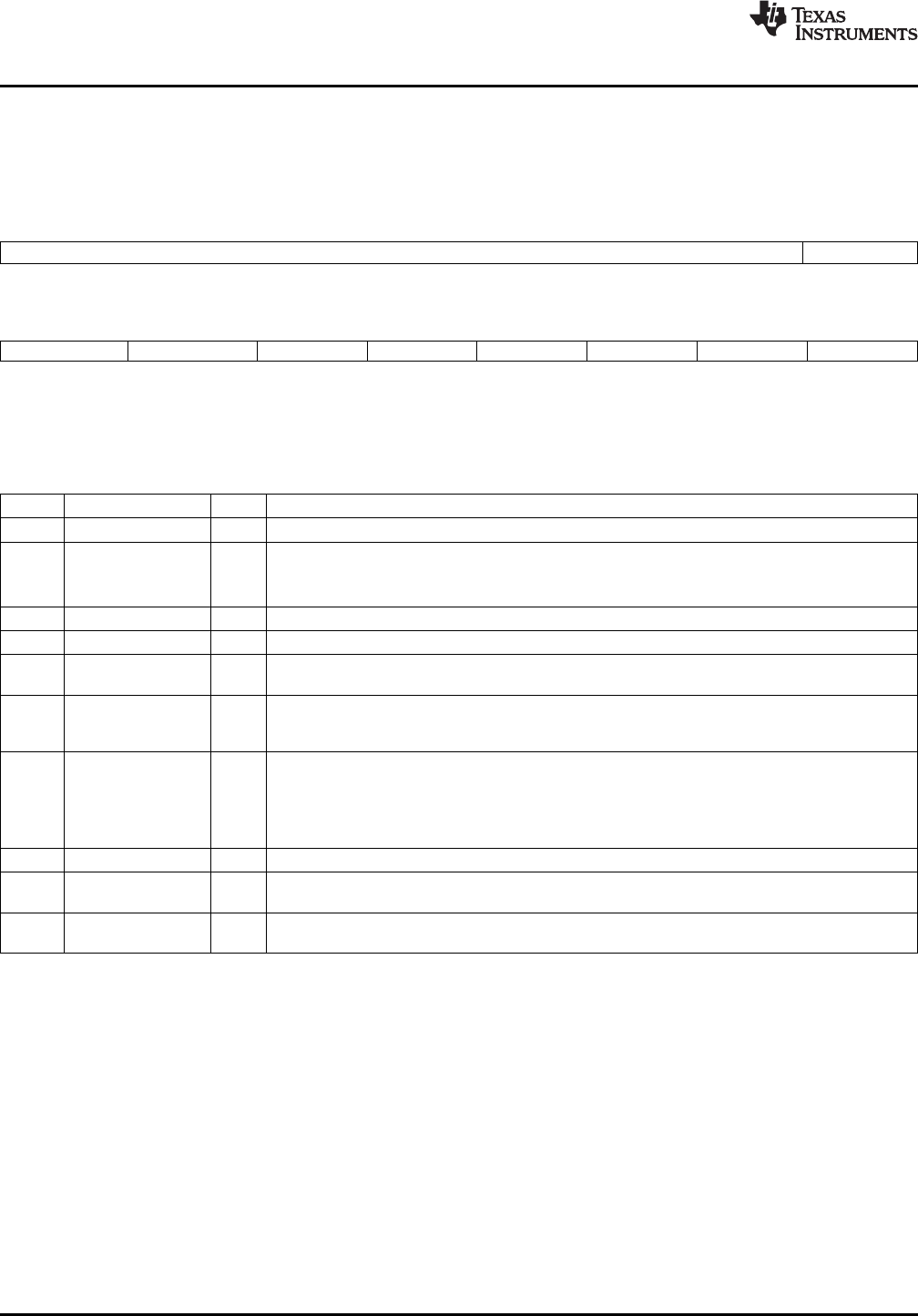

TheControlStatusRegisterforEndpoint0inPeripheralMode(PERI_CSR0)isshowninFigure72and

describedinTable73.

Figure72.ControlStatusRegisterforEndpoint0inPeripheralMode(PERI_CSR0)

1598

ReservedFLUSHFIFO

R-0W-0

76543210

SERV_SETUPENDSERV_RXPKTRDYSENDSTALLSETUPENDDATAENDSENTSTALLTXPKTRDYRXPKTRDY

W-0W-0W-0R-0W-0R/W-0R/W-0R-0

LEGEND:R/W=Read/Write;R=Readonly;W=Writeonly;-n=valueafterreset

Table73.ControlStatusRegisterforEndpoint0inPeripheralMode(PERI_CSR0)

FieldDescriptions

BitFieldValueDescription

15-9Reserved0Reserved

8FLUSHFIFO0-1Setthisbittoflushthenextpackettobetransmitted/readfromtheEndpoint0FIFO.TheFIFO

pointerisresetandtheTXPKTRDY/RXPKTRDYbitiscleared.

Note:FLUSHFIFOhasnoeffectunlessTXPKTRDY/RXPKTRDYisset.

7SERV_SETUPEND0-1SetthisbittocleartheSETUPENDbit.Itisclearedautomatically.

6SERV_RXPKTRDY0-1SetthisbittocleartheRXPKTRDYbit.Itisclearedautomatically.

5SENDSTALL0-1Setthisbittoterminatethecurrenttransaction.TheSTALLhandshakewillbetransmittedand

thenthisbitwillbeclearedautomatically.

4SETUPEND0-1ThisbitwillbesetwhenacontroltransactionendsbeforetheDATAENDbithasbeenset.An

interruptwillbegenerated,andtheFIFOwillbeflushedatthistime.Thebitisclearedbythe

writinga1totheSERV_SETUPENDbit.

3DATAEND0-1Setthisbitto:

1-WhensettingTXPKTRDYforthelastdatapacket

2-WhenclearingRXPKTRDYafterunloadingthelastdatapacket

3-WhensettingTXPKTRDYforazerolengthdatapacket.Itisclearedautomatically.

2SENTSTALL0-1ThisbitissetwhenaSTALLhandshakeistransmitted.Thisbitshouldbecleared.

1TXPKTRDY0-1SetthisbitafterloadingadatapacketintotheFIFO.Itisclearedautomaticallywhenthedata

packethasbeentransmitted.Aninterruptisgenerated(ifenabled)whenthebitiscleared.

0RXPKTRDY0-1Thisbitissetwhenadatapackethasbeenreceived.Aninterruptisgeneratedwhenthisbitisset.

ThisbitisclearedbysettingtheSERV_RXPKTRDYbit.

UniversalSerialBus(USB)Controller 120SPRUGH3–November2008

SubmitDocumentationFeedback