4.63ControlStatusRegisterforHostReceiveEndpoint(HOST_RXCSR)

Registers

www.ti.com

TheControlStatusRegisterforHostReceiveEndpoint(HOST_RXCSR)isshowninFigure78and

describedinTable79.

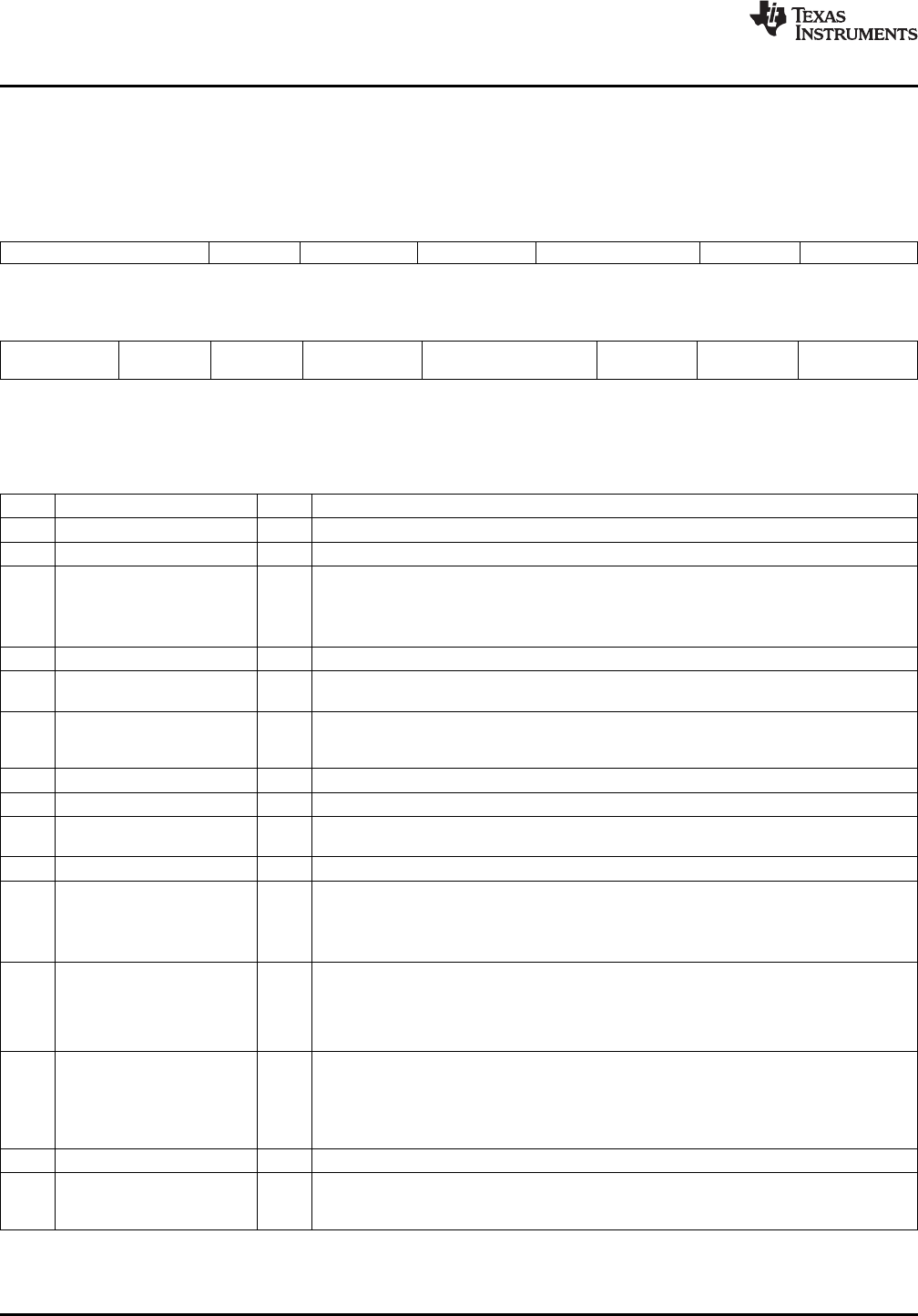

Figure78.ControlStatusRegisterforHostReceiveEndpoint(HOST_RXCSR)

15141312111098

ReservedDMAENDISNYETDMAMODEDATATOGWRENDATATOGReserved

R-0R/W-0R/W-0R/W-0W-0R/W-0R-0

76543210

CLRDATATOGRXSTALLREQPKTFLUSHFIFODATAERR_NAKERRORFIFOFULLRXPKTRDY

TIMEOUT

W-0R/W-0R/W-0W-0R-0R/W-0R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;W=Writeonly;-n=valueafterreset

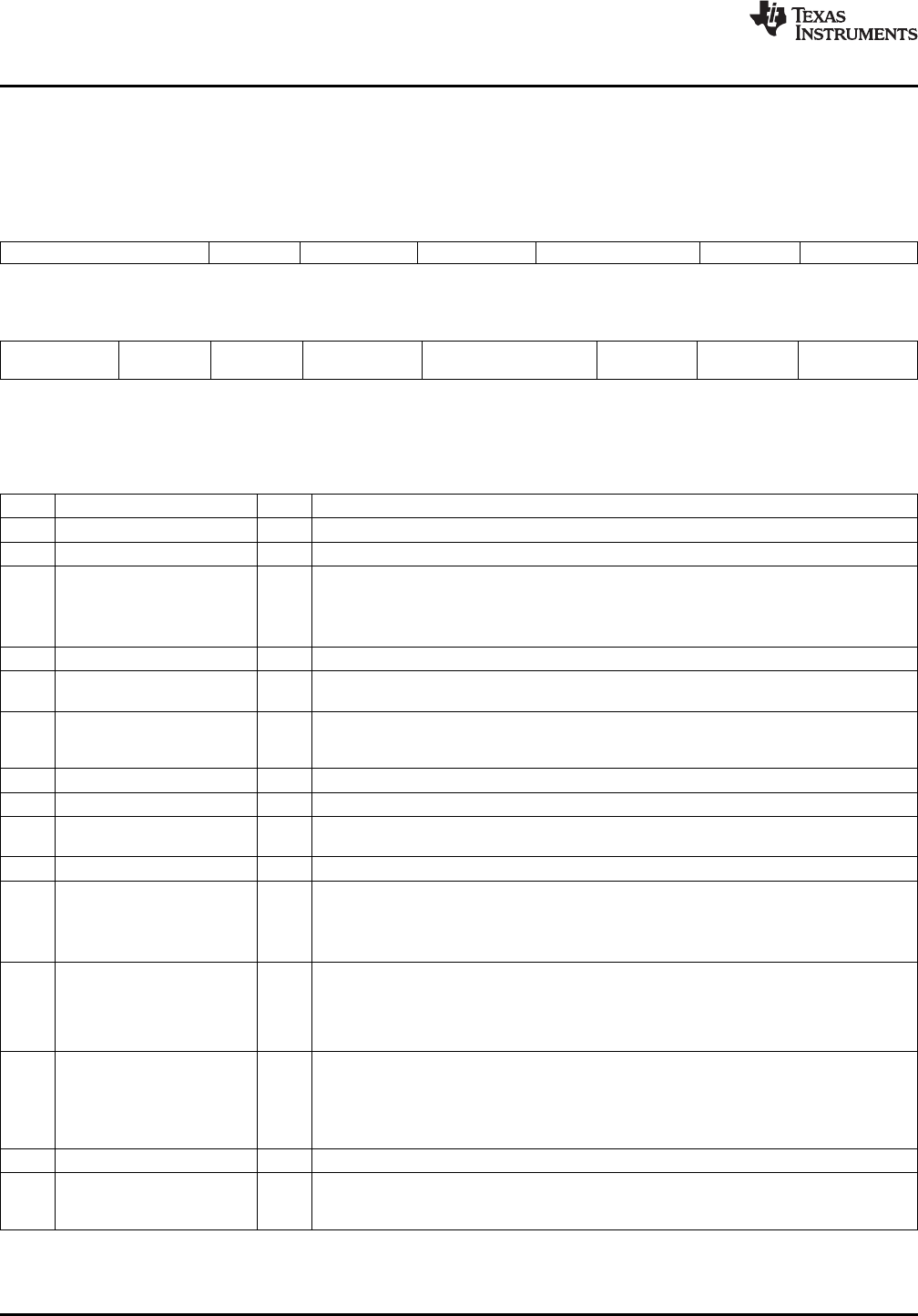

Table79.ControlStatusRegisterforHostReceiveEndpoint(HOST_RXCSR)FieldDescriptions

BitFieldValueDescription

15-14Reserved0Reserved

13DMAEN0-1SetthisbittoenabletheDMArequestfortheReceiveendpoints.

12DISNYET0-1SetthisbittodisablethesendingofNYEThandshakes.Whenset,allsuccessfullyreceived

ReceivepacketsareACKEDincludingatthepointatwhichtheFIFObecomesfull.

Note:Thisbitonlyhasanyeffectinhigh-speedmode,inwhichmodeitshouldbesetforall

Interruptendpoints.

11DMAMODE0Thisbitshouldalwaysbeclearedto0.

10DATATOGWREN0-1SetthisbittoenabletheDATATOGbittobewritten.Thisbitisautomaticallyclearedonce

thenewvalueiswrittentoDATATOG.

9DATATOG0-1Whenread,thisbitindicatesthecurrentstateoftheReceiveEPdatatoggle.If

DATATOGWRENishigh,thisbitcanbewrittenwiththerequiredsettingofthedatatoggle.

IfDATATOGWRENislow,anyvaluewrittentothisbitisignored.

8Reserved0Reserved

7CLRDATATOG0-1Setthisbittoresettheendpointdatatoggleto0.

6RXSTALL0-1WhenaSTALLhandshakeisreceived,thisbitissetandaninterruptisgenerated.You

shouldclearthisbit.

5REQPKT0-1SetthisbittorequestanINtransaction.ItisclearedwhenRXPKTRDYisset.

4FLUSHFIFO0-1SetthisbittoflushthenextpackettobereadfromtheendpointReceiveFIFO.TheFIFO

pointerisresetandtheRXPKTRDYbitiscleared.

Note:FLUSHFIFOhasnoeffectunlessRXPKTRDYisset.Alsonotethat,iftheFIFOis

double-buffered,FLUSHFIFOmayneedtobesettwicetocompletelycleartheFIFO.

3DATAERR_NAKTIMEOUT0-1WhenoperatinginISOmode,thisbitissetwhenRXPKTRDYissetifthedatapackethas

aCRCorbit-stufferrorandclearedwhenRXPKTRDYiscleared.InBulkmode,thisbitwill

besetwhentheReceiveendpointishaltedfollowingthereceiptofNAKresponsesfor

longerthanthetimesetastheNAKLimitbytheRXINTERVALregister.Youshouldclear

thisbittoallowtheendpointtocontinue.

2ERROR0-1TheUSBcontrollersetsthisbitwhen3attemptshavebeenmadetoreceiveapacketand

nodatapackethasbeenreceived.Youshouldclearthisbit.Aninterruptisgeneratedwhen

thebitisset.

Note:ThisbitisonlyvalidwhenthetransmitendpointisoperatinginBulkorInterrupt

mode.InISOmode,italwaysreturnszero.

1FIFOFULL0-1ThisbitissetwhennomorepacketscanbeloadedintotheReceiveFIFO.

0RXPKTRDY0-1Thisbitissetwhenadatapackethasbeenreceived.Youshouldclearthisbitwhenthe

packethasbeenunloadedfromtheReceiveFIFO.Aninterruptisgeneratedwhenthebitis

set.

UniversalSerialBus(USB)Controller 126SPRUGH3–November2008

SubmitDocumentationFeedback