3.2.2BulkTransactions

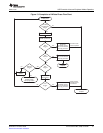

3.2.2.1HostMode:BulkINTransactions

USBControllerHostandPeripheralModesOperation

www.ti.com

ABulkINtransactionmaybeusedtotransfernon-periodicdatafromtheexternalUSBperipheraltothe

host.

ThefollowingoptionalfeaturesareavailableforusewithanRxendpointusedinhostmodetoreceivethe

data:

•Doublepacketbuffering:Whenenabled,uptotwopacketscanbestoredintheFIFOonreception

fromthehost.Thisallowsthatonepacketcanbereceivedwhileanotherisbeingread.Doublepacket

bufferingisenabledbysettingtheDPBbitofRXFIFOSZregister(bit4).

•DMA:IfDMAisenabledfortheendpoint,aDMArequestwillbegeneratedwhenevertheendpointhas

apacketinitsFIFO.ThisfeaturecanbeusedtoallowtheDMAcontrollertounloadpacketsfromthe

FIFOwithoutprocessorintervention.

WhenDMAisenabled,endpointinterruptwillnotbegeneratedforcompletionofpacketreception.

Endpointinterruptwillbegeneratedonlyintheerrorconditions.

•AutoRequest:WhentheAutoRequestfeatureisenabled,theREQPKTbitofHOST_RXCSR(bit5)will

beautomaticallysetwhentheRXPKTRDYbitiscleared.

ThisfeatureisapplicableonlywhenDMAisenabled.ToenableAutoRequestfeature,setthe

AUTOREQregisterfortheDMAchannelassociatedfortheendpoint.

3.2.2.1.1Setup

BeforeinitiatinganyBulkINTransactionsinHostmode:

•ThetargetfunctionaddressneedstobesetintheRXFUNCADDRregisterfortheselectedcontroller

endpoint.(RXFUNCADDRregisterisavailableforallendpointsfromEP0toEP4.)

•TheHOST_RXTYPEregisterfortheendpointthatistobeusedneedstobeprogrammedasfollows:

–OperatingspeedintheSPEEDbitfield(bits7and6).

–Set10(binaryvalue)inthePROTfieldforbulktransfer.

–EndpointNumberofthetargetdeviceinRENDPNfield.Thisistheendpointnumbercontainedin

theRxendpointdescriptorreturnedbythetargetdeviceduringenumeration.

•TheRXMAXPregisterforthecontrollerendpointmustbewrittenwiththemaximumpacketsize(in

bytes)forthetransfer.ThisvalueshouldbethesameasthewMaxPacketSizefieldoftheStandard

EndpointDescriptorforthetargetendpoint.

•TheHOST_RXINTERVALregisterneedstobewrittenwiththerequiredvaluefortheNAKlimit(2-215

frames/microframes),orclearedto0iftheNAKtimeoutfeatureisnotrequired.

•TherelevantinterruptenablebitintheINTRRXEregistershouldbeset(ifaninterruptisrequiredfor

thisendpoint).

•ThefollowingbitsofHOST_RXCSRregistershouldbesetasshownbelow:

–SetDMAEN(bit13)to1ifaDMArequestisrequiredforthisendpoint.

–ClearDSINYET(bit12)to0toallownormalPINGflowcontrol.ThiswillaffectonlyHighSpeed

transactions.

–AlwaysclearDMAMODE(bit11)to0.

•IfDMAisenabled,theAUTOREQregistercanbesetforgeneratingINtokensautomaticallyafter

receivingthedata.SetthebitfieldRXn_AUTOREQ(wherenistheendpointnumber)withbinaryvalue

01or11.

Whentheendpointisfirstconfigured,theendpointdatatoggleshouldbeclearedto0eitherbyusingthe

DATATOGWRENandDATATOGbitsofHOST_RXCSR(bit10andbit9)totogglethecurrentsettingor

bysettingtheCLRDATATOGbitofHOST_RXCSR(bit7).Thiswillensurethatthedatatoggle(whichis

handledautomaticallybythecontroller)startsinthecorrectstate.Alsoifthereareanydatapacketsinthe

FIFO(indicatedbytheRXPKTRDYbit(bit0ofHOST_RXCSR)beingset),theyshouldbeflushedby

settingtheFLUSHFIFObitofHOST_RXCSR(bit4).

Note:Itmaybenecessarytosetthisbittwiceinsuccessionifdoublebufferingisenabled.

UniversalSerialBus(USB)Controller 52SPRUGH3–November2008

SubmitDocumentationFeedback