4.1ControlRegister(CTRLR)

Registers

www.ti.com

Table16.UniversalSerialBus(USB)Registers(continued)

OffsetAcronymRegisterDescriptionSection

546hPERI_RXCSRControlStatusRegisterforPeripheralReceiveEndpointSection4.62

(peripheralmode)

HOST_RXCSRControlStatusRegisterforHostReceiveEndpointSection4.63

(hostmode)

548hRXCOUNTNumberofBytesinHostReceiveendpointFIFOSection4.65

54AhHOST_TXTYPESetstheoperatingspeed,transactionprotocolandperipheralSection4.67

endpointnumberforthehostTransmitendpoint.

54BhHOST_TXINTERVALSetsthepollingintervalforInterrupt/ISOCtransactionsortheSection4.69

NAKresponsetimeoutonBulktransactionsforhostTransmit

endpoint.

54ChHOST_RXTYPESetstheoperatingspeed,transactionprotocolandperipheralSection4.70

endpointnumberforthehostReceiveendpoint.

54DhHOST_RXINTERVALSetsthepollingintervalforInterrupt/ISOCtransactionsortheSection4.71

NAKresponsetimeoutonBulktransactionsforhostReceive

endpoint.

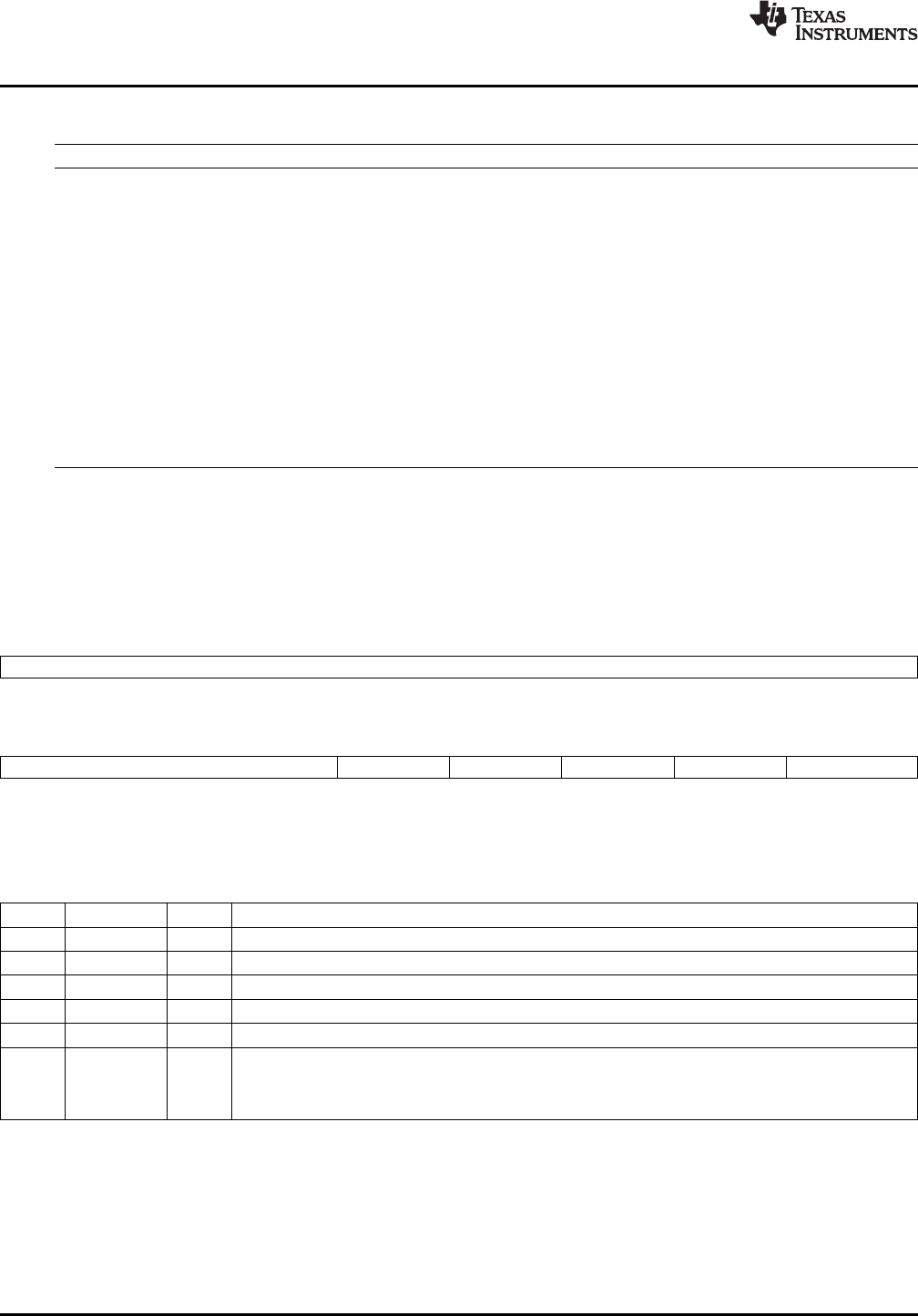

TheControlRegister(CTRLR)isshowninFigure16anddescribedinTable17.

Figure16.ControlRegister(CTRLR)

3116

Reserved

R-0

15543210

ReservedRNDISUINTReservedCLKFACKRESET

R-0R/W-0R/W-0R-0R/W-0W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table17.ControlRegister(CTRLR)FieldDescriptions

BitFieldValueDescription

31-5Reserved0Reserved

4RNDIS0-1RNDISmodeenable.

3UINT0-1USBnon-PDRinterruptenable.

2Reserved0Reserved

1CLKFACK0-1ClockstopfastACKenable.

0RESETSoftreset.

0

1Writinga1startsamodulereset.

UniversalSerialBus(USB)Controller 82SPRUGH3–November2008

SubmitDocumentationFeedback