4.2StatusRegister(STATR)

4.3RNDISRegister(RNDISR)

www.ti.com

Registers

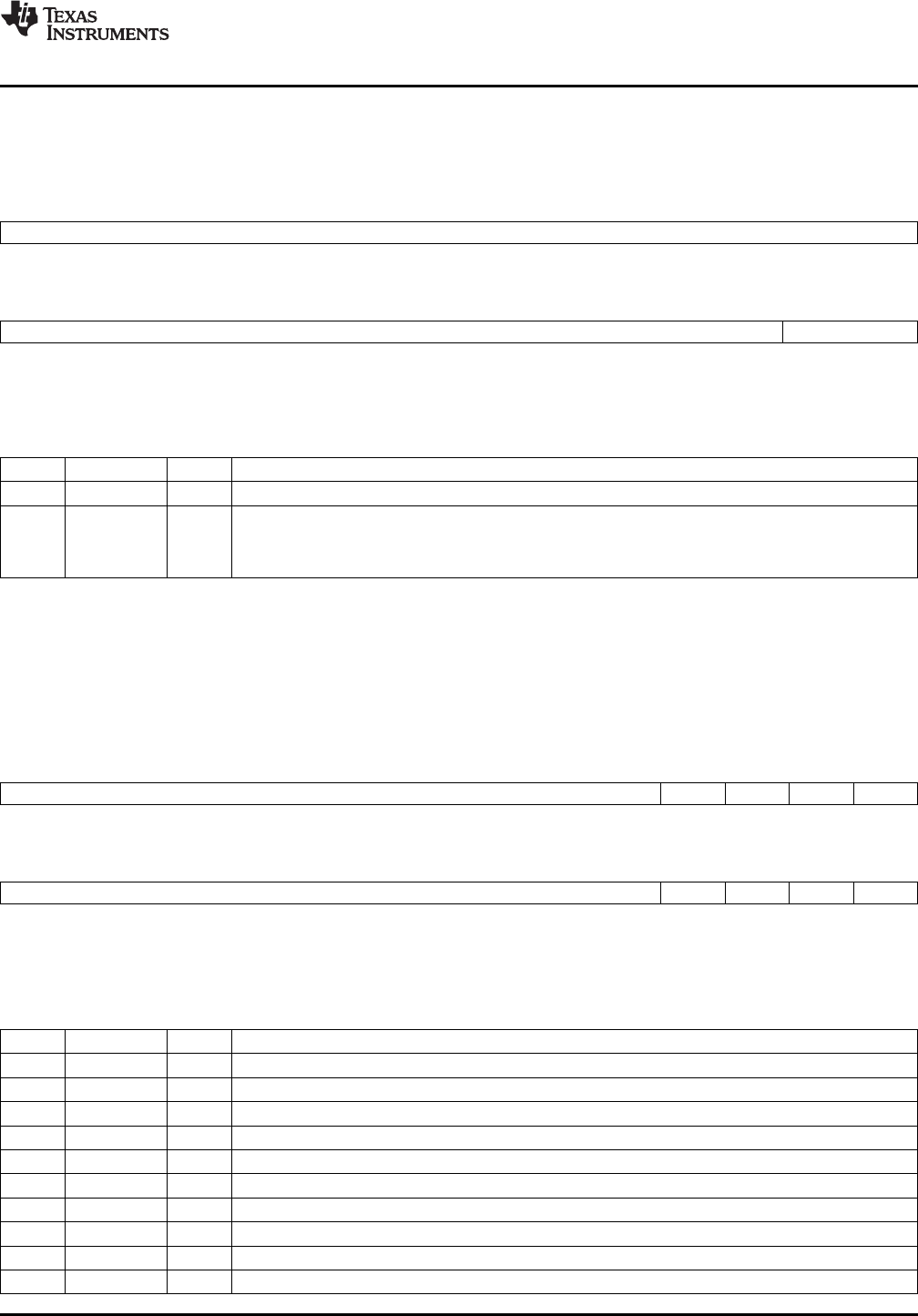

TheStatusRegister(STATR)isshowninFigure17anddescribedinTable18.

Figure17.StatusRegister(STATR)

3116

Reserved

R-0

1510

ReservedDRVVBUS

R-0R-0

LEGEND:R=Readonly;-n=valueafterreset

Table18.StatusRegister(STATR)FieldDescriptions

BitFieldValueDescription

31-1Reserved0Reserved

0DRVVBUSCurrentDRVVBUSvalue.

0DRVVBUSvalueislogic0

1DRVVBUSvalueislogic1

TheRNDISRegister(RNDISR)isshowninFigure18anddescribedinTable19.

Figure18.RNDISRegister(RNDISR)

312019181716

ReservedRX4ENRX3ENRX2ENRX1EN

R-0R/W-0R/W-0R/W-0R/W-0

1543210

ReservedTX4ENTX3ENTX2ENTX1EN

R-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table19.RNDISRegister(RNDISR)FieldDescriptions

BitFieldValueDescription

31-20Reserved0Reserved

19RX4EN0-1ReceiveEndpoint4RNDISmodeenable.

18RX3EN0-1ReceiveEndpoint3RNDISmodeenable.

17RX2EN0-1ReceiveEndpoint2RNDISmodeenable.

16RX1EN0-1ReceiveEndpoint1RNDISmodeenable.

15-4Reserved0Reserved

3TX4EN0-1TransmitEndpoint4RNDISmodeenable.

2TX3EN0-1TransmitEndpoint3RNDISmodeenable.

1TX2EN0-1TransmitEndpoint2RNDISmodeenable.

0TX1EN0-1TransmitEndpoint1RNDISmodeenable.

SPRUGH3–November2008UniversalSerialBus(USB)Controller83

SubmitDocumentationFeedback