4.58ControlStatusRegisterforEndpoint0inHostMode(HOST_CSR0)

www.ti.com

Registers

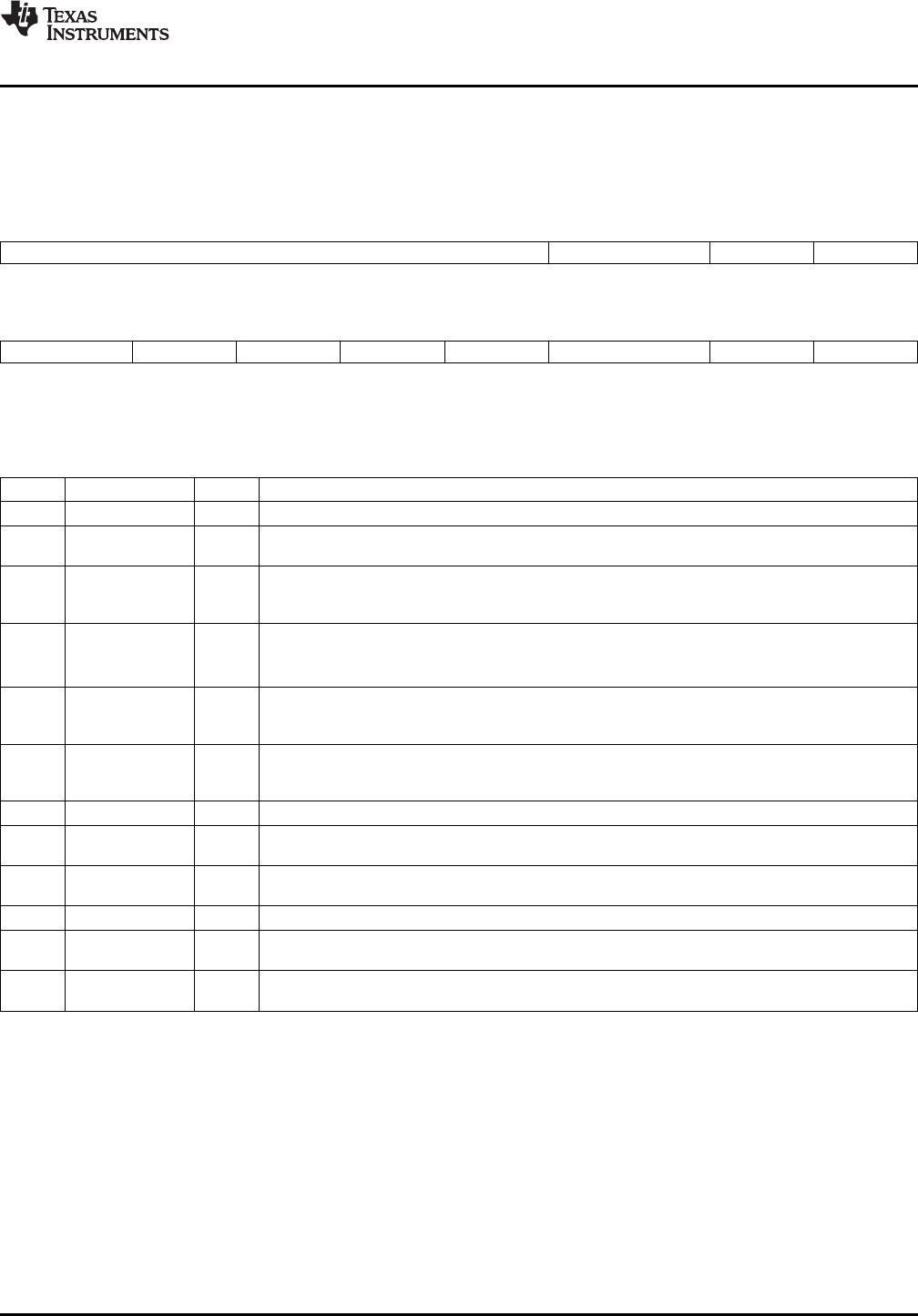

TheControlStatusRegisterforEndpoint0inHostMode(HOST_CSR0)isshowninFigure73and

describedinTable74.

Figure73.ControlStatusRegisterforEndpoint0inHostMode(HOST_CSR0)

15111098

ReservedDATATOGWRENDATATOGFLUSHFIFO

R-0W-0R/W-0W-0

76543210

NAK_TIMEOUTSTATUSPKTREQPKTERRORSETUPPKTRXSTALLTXPKTRDYRXPKTRDY

W-0R/W-0R/W-0W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;W=Writeonly;-n=valueafterreset

Table74.ControlStatusRegisterforEndpoint0inHostMode(HOST_CSR0)FieldDescriptions

BitFieldValueDescription

15-11Reserved0Reserved

10DATATOGWREN0-1SetthisbittoenabletheDATATOGbittobewritten.Thisbitisautomaticallyclearedoncethenew

valueiswrittentoDATATOG.

9DATATOG0-1Whenread,thisbitindicatesthecurrentstateoftheEP0datatoggle.IfDATATOGWRENishigh,

thisbitcanbewrittenwiththerequiredsettingofthedatatoggle.IfDATATOGWRENislow,any

valuewrittentothisbitisignored.

8FLUSHFIFO0-1Setthisbittoflushthenextpackettobetransmitted/readfromtheEndpoint0FIFO.TheFIFO

pointerisresetandtheTXPKTRDY/RXPKTRDYbitiscleared.

Note:FLUSHFIFOhasnoeffectunlessTXPKTRDY/RXPKTRDYisset.

7NAK_TIMEOUT0-1ThisbitwillbesetwhenEndpoint0ishaltedfollowingthereceiptofNAKresponsesforlongerthan

thetimesetbytheNAKLIMIT0register.Thisbitshouldbeclearedtoallowtheendpointto

continue.

6STATUSPKT0-1SetthisbitatthesametimeastheTXPKTRDYorREQPKTbitisset,toperformastatusstage

transaction.SettingthisbitensuresthatthedatatoggleissetsothataDATA1packetisusedfor

theStatusStagetransaction.

5REQPKT0-1SetthisbittorequestanINtransaction.ItisclearedwhenRXPKTRDYisset.

4ERROR0-1Thisbitwillbesetwhenthreeattemptshavebeenmadetoperformatransactionwithnoresponse

fromtheperipheral.Youshouldclearthisbit.Aninterruptisgeneratedwhenthisbitisset.

3SETUPPKT0-1Setthisbit,atthesametimeastheTXPKTRDYbitisset,tosendaSETUPtokeninsteadofan

OUTtokenforthetransaction.

2RXSTALL0-1ThisbitissetwhenaSTALLhandshakeisreceived.Youshouldclearthisbit.

1TXPKTRDY0-1SetthisbitafterloadingadatapacketintotheFIFO.Itisclearedautomaticallywhenthedata

packethasbeentransmitted.Aninterruptisgenerated(ifenabled)whenthebitiscleared.

0RXPKTRDY0-1Thisbitissetwhenadatapackethasbeenreceived.Aninterruptisgeneratedwhenthisbitisset.

ClearthisbitbysettingtheSERV_RXPKTRDYbit.

SPRUGH3–November2008UniversalSerialBus(USB)Controller121

SubmitDocumentationFeedback