10006757-02 PmPPC7448 User’s Manual

3-1

Section 3

Central Processing Unit

This chapter is an overview of the processor logic on the PmPPC7448. It includes informa-

tion on the CPU, exception handling, and cache memory. The PmPPC7448 utilizes the Free-

scale MPC7448 RISC microprocessor, for more detailed information reference the Freescale

Semiconductor MPC7450 RISC Microprocessor Family User’s Manual.

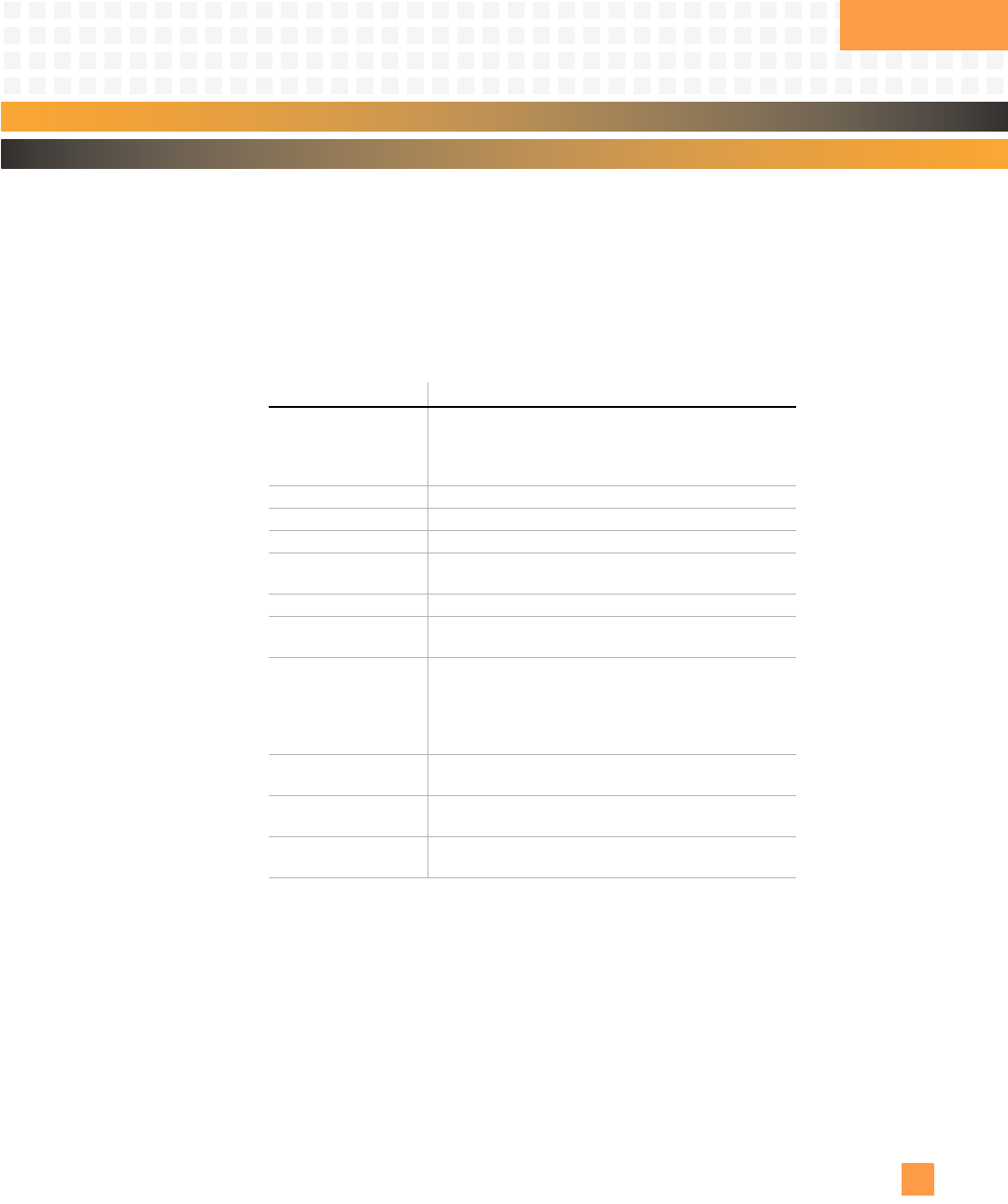

The following table outlines some of the key features for the MPC7448 CPU.

Table 3-1: PmPPC7448 CPU Features

Category: MPC7448 Key Features:

Instruction Set Up to three instructions can be dispatched, four

instructions can be fetched, 12 instructions can be in

the queue, and 16 instructions can be at some stage of

execution

CPU Speed (Internal) Up to 1.4 GHz

Data Bus 64-bit with 8 bits of data parity

Address Bus 36-bit with 5 bits of address parity

Seven Stage Pipeline

Control

Fetch, dispatch/decode, execute, complete/write

back

L1 Cache 32 kilobytes instruction, 32 kilobytes data

L2 Cache 1 megabyte, eight-way set-associative unified

instruction and data cache, ECC capability

Execution Units Branch processing (BPU), four integer (IU), 64-bit

floating-point (FPU), four vector (VPU, VIU1, VIU2,

VFPU), three-stage load/store (LSU), three issue

queues (FIQ, VIQ, GIQ), rename buffers, dispatch, and

completion

Memory

Management Units

52-bit virtual address, 32- or 36-bit physical address

Voltages Processor core, 1.0 V at 1.0 GHz or lower,

1.15 V at 1.4 GHz

Power Management Dynamic Frequency Switching capability (divide-by-

two and divide-by-four modes)