Central Processing Unit: Cache Memory

10006757-02 PmPPC7448 User’s Manual

3-11

L2 Cache

The internal 1 megabyte L2 cache is an eight-way set associative instruction and data cache

with ECC capability. The L2 cache is fully pipelined to provide 32 bytes per clock to the L1

caches. The L2 Cache Control register (L2CR) configures and operates the L2 cache. The

L2CR is read/write and contents are cleared during power-on reset.

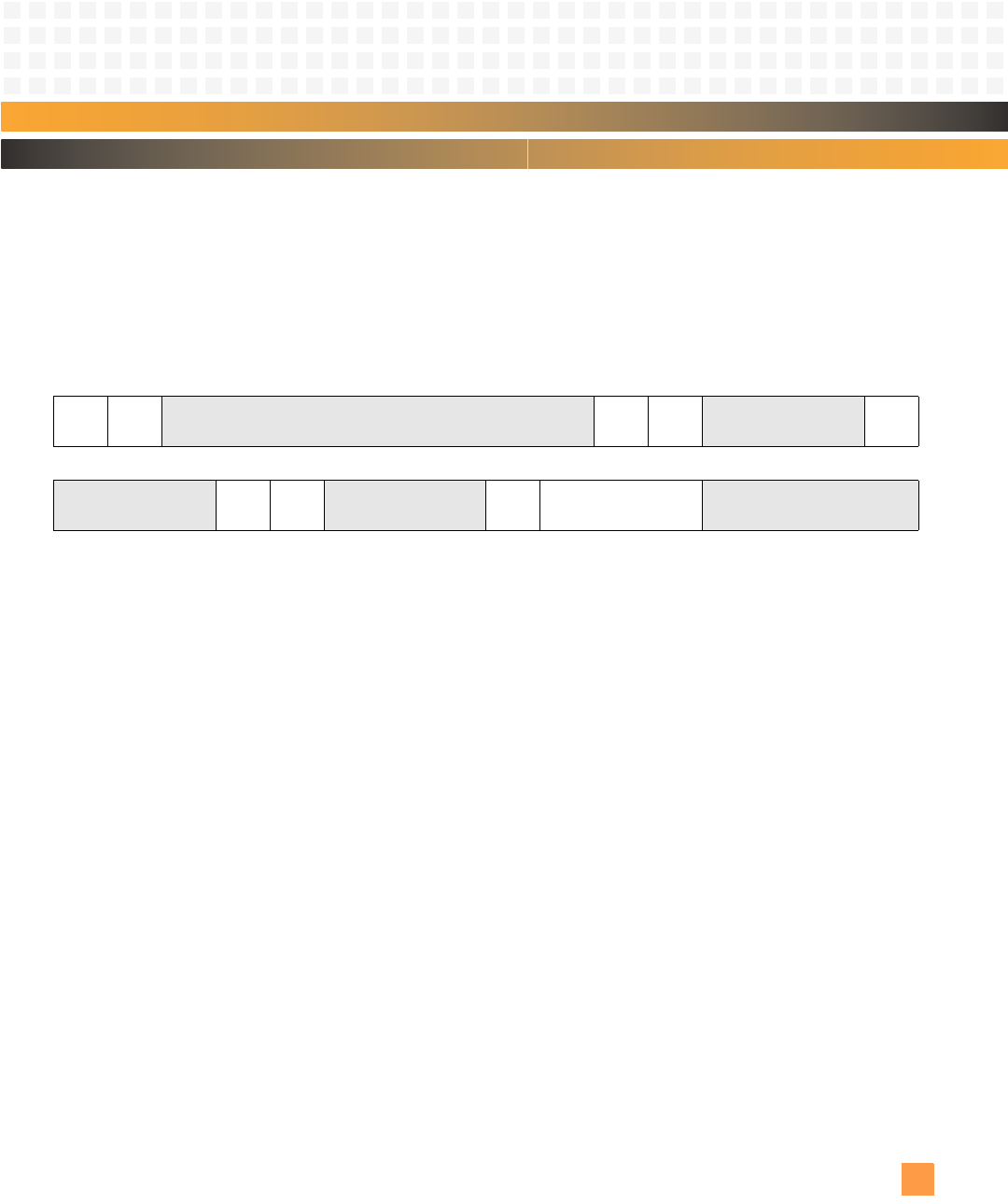

Register 3-4: L2 Cache Control Register (L2CR)

L2E: L2 Cache enable—enables and disables the operation of the L2 cache, starting with the next

transaction.

0 Operation disabled

1Operation enabled

L2PE: L2 Data Parity Checking enable

0 L2 parity checking disabled

1 L2 parity checking enabled

L2I: L2 Global Invalidate—setting this bit invalidates the L2 cache globally by clearing the L2 sta-

tus bits.

0 Not invalidated globally

1 Invalidated globally

L2IO: L2 Instruction-Only mode—for this operation, only instruction accesses cause new entries to

be allocated in the L2 cache.

0Operation enabled

1 Operation disabled

L2DO: L2 Data-Only mode—for this operation, only data accesses cause new entries to be allocated

in the L2 cache.

0Operation enabled

1 Operation disabled

L2REP: L2 Replacement Algorithm

0 Pseudo-random replacement algorithm is used (default)

1 3-bit counter replacement algorithm is used

0 1 2 9 101112 1415

L2E L2PE reserved L2I L2IO R

L2D

O

16 18 19 20 21 23 24 25 27 28 31

R

L2

REP

L2

HWF

R

LVR

AME

LVRAMM

reserved