Functional Description

R

Intel

®

82845 MCH for SDR Datasheet 115

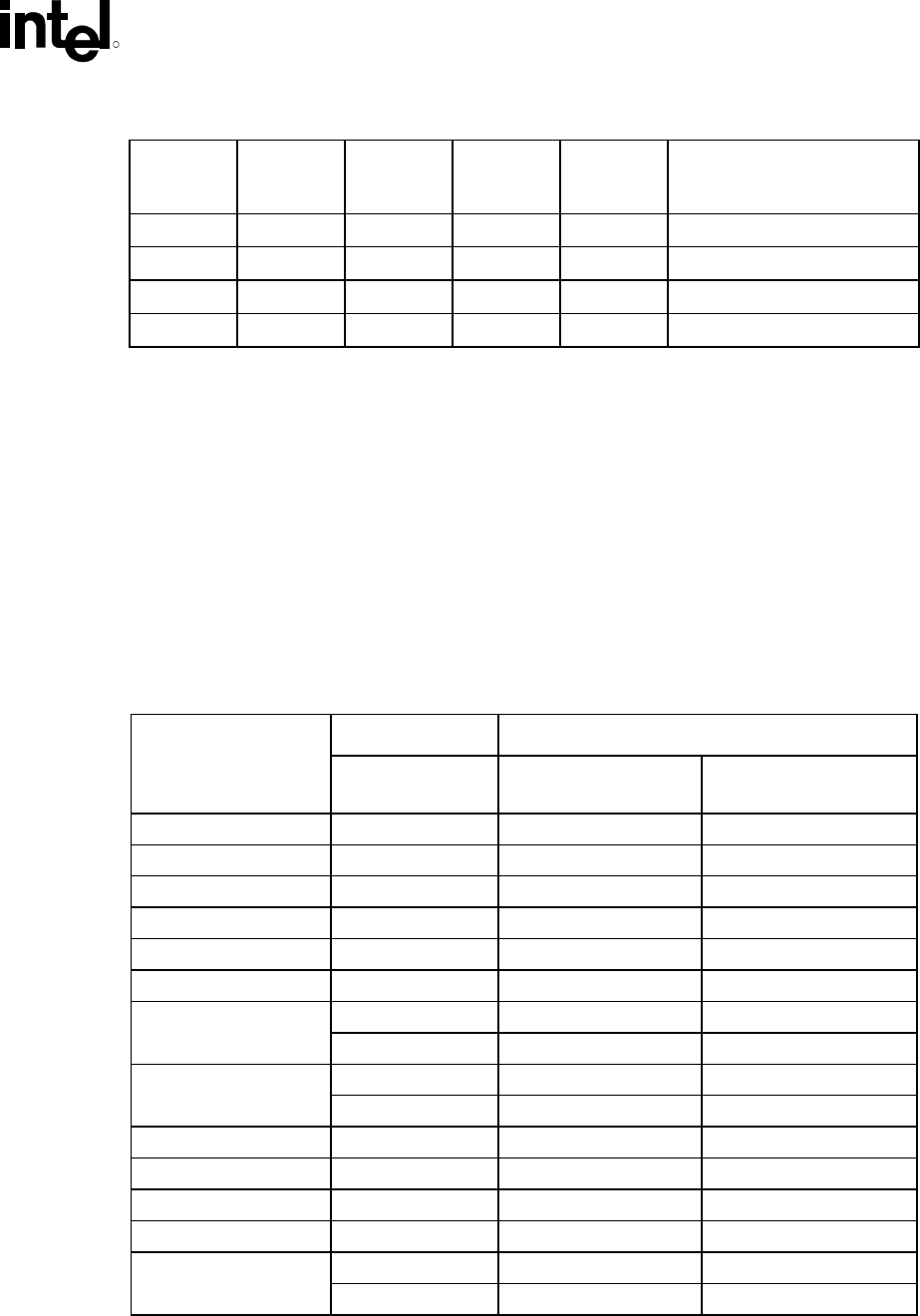

Table 16. Data Rate Control Bits

AGPCNTL

.FWCE

AGPCMD.

FWPE

AGPCMD.

DRATE

[bit 2]

AGPCMD.

DRATE

[bit 1]

AGPCMD.

DRATE

[bit 0]

MCH =>AGP Master Write

Protocol

0 0 X X X 1x

1 1 0 0 1 1x

1 1 0 1 0 2x strobing

1 1 1 0 0 4x strobing

5.3.6 AGP FRAME# Transactions on AGP

The MCH accepts and generates AGP FRAME# transactions on the AGP bus. The MCH

guarantees that AGP FRAME# accesses to system memory are kept coherent with the processor

caches by generating snoops to the host bus. LOCK#, SERR#, and PERR# signals are not

supported.

MCH Initiator and Target Operations

Table 17 summarizes MCH target operation for AGP FRAME# initiators. The cycles can be either

destined to system memory or the hub interface.

Table 17. PCI Commands Supported by the Intel

®

MCH (When Acting as a FRAME# Target)

C/BE[3:0]# Intel

®

MCH PCI Command

Encoding Cycle Destination Response as a FRAME#

Target

Interrupt Acknowledge 0000 N/A No response

Special cycle 0001 N/A No response

I/O Read 0010 N/A No response

I/O Write 0011 N/A No response

Reserved 0100 N/A No response

Reserved 0101 N/A No response

Memory Read 0110 System memory Read

0110 Hub interface No response

Memory Write 0111 System memory Posts data

0111 Hub interface No response

Reserved 1000 N/A No response

Reserved 1001 N/A No response

Configuration Read 1010 N/A No response

Configuration Write 1011 N/A No response

Memory Read Multiple 1100 System memory Read

1100 Hub interface No response