Testability

R

138 Intel

®

82845 MCH for SDR Datasheet

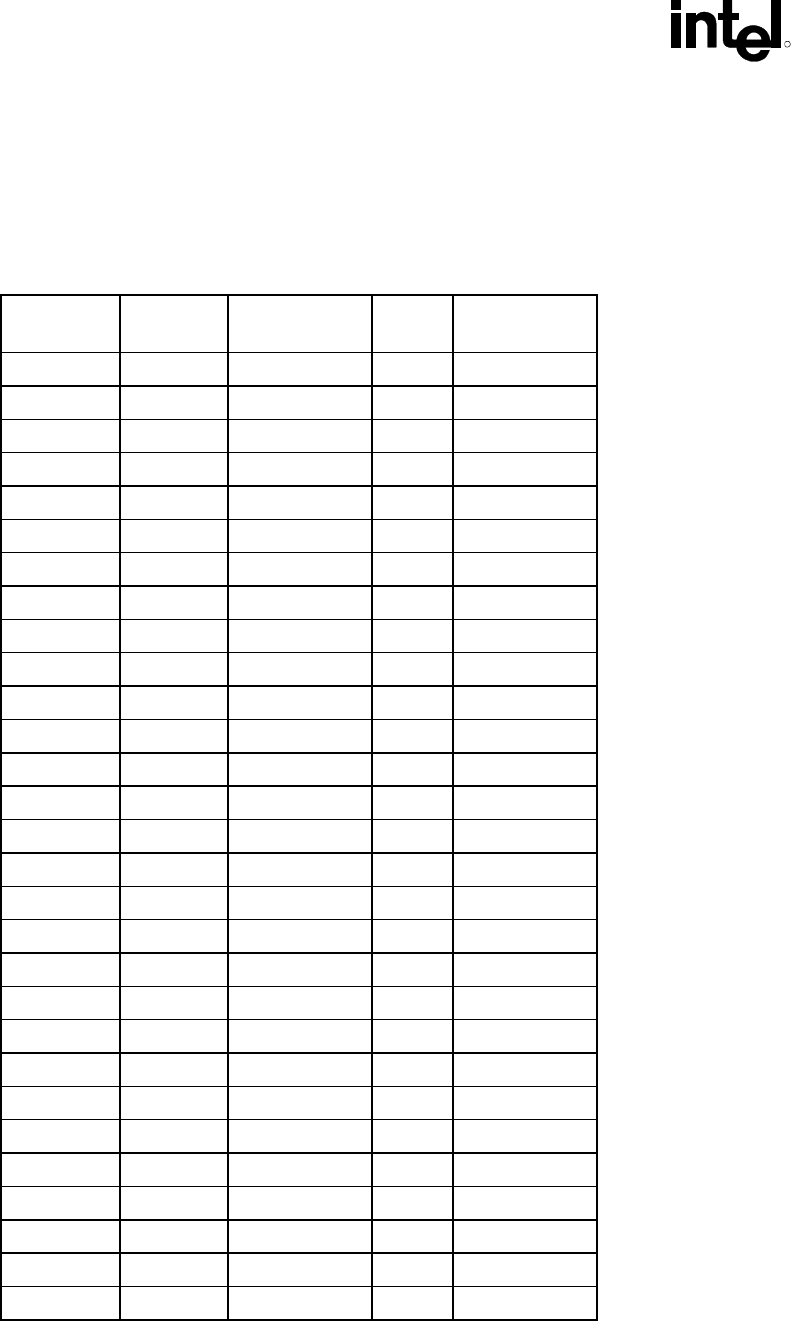

8.2 XOR Chains

Note: RSTIN#, TESTIN#, and all Rcomp buffers are not part of any XOR chain.

Table 23. XOR Chain 0

Chain 0 Ball Element # Signal Name Note Initial Logic

Level

AE6 1 HDSTBP1# Input 1

AD3 2 HDSTBP0# Input 1

V3 3 ADS# Input 1

U6 4 HREQ0# Input 1

U3 5 HA6# Input 1

U2 6 HREQ4# Input 1

U5 7 HREQ3# Input 1

T5 8 HA4# Input 1

T7 9 HREQ1# Input 1

T4 10 HA3# Input 1

R7 11 HREQ2# Input 1

R5 12 HADSTB0# Input 1

R3 13 HA7# Input 1

P3 14 HA13# Input 1

R2 15 HA9# Input 1

R6 16 HA11# Input 1

T3 17 HA5# Input 1

N3 18 HA16# Input 1

P5 19 HA12# Input 1

P4 20 HA10# Input 1

P7 21 HA8# Input 1

N2 23 HA14# Input 1

N7 24 HA15# Input 1

N5 25 HA28# Input 1

M4 26 HA18# Input 1

L3 27 HA20# Input 1

M3 28 HA19# Input 1

L2 29 HA26# Input 1

K3 30 HA22# Input 1