System Address Map

R

Intel

®

82845 MCH for SDR Datasheet 97

4 System Address Map

A system based on the 845 chipset supports 4 GB of addressable memory space and 64 KB+3 of

addressable I/O space. The I/O and memory spaces are divided by system configuration software

into regions. The memory ranges are useful either as system memory or as specialized memory,

while the I/O regions are used solely to control the operation of devices in the system.

When the MCH receives a write request whose address targets an invalid space, the data is

ignored. For reads, the MCH responds by returning all zeros on the requesting interface.

4.1 Memory Address Ranges

The system memory map is broken into two categories:

• Extended Memory Range (1 MB to 4 GB). The second is extended memory, existing

between 1MB and 4GB. It contains a 32-bit memory space, which is used for mapping PCI,

AGP, APIC, SMRAM, and BIOS memory spaces.

• DOS Compatible Area (below 1 MB). The final range is a DOS legacy space, which is used

for BIOS and legacy devices on the LPC interface.

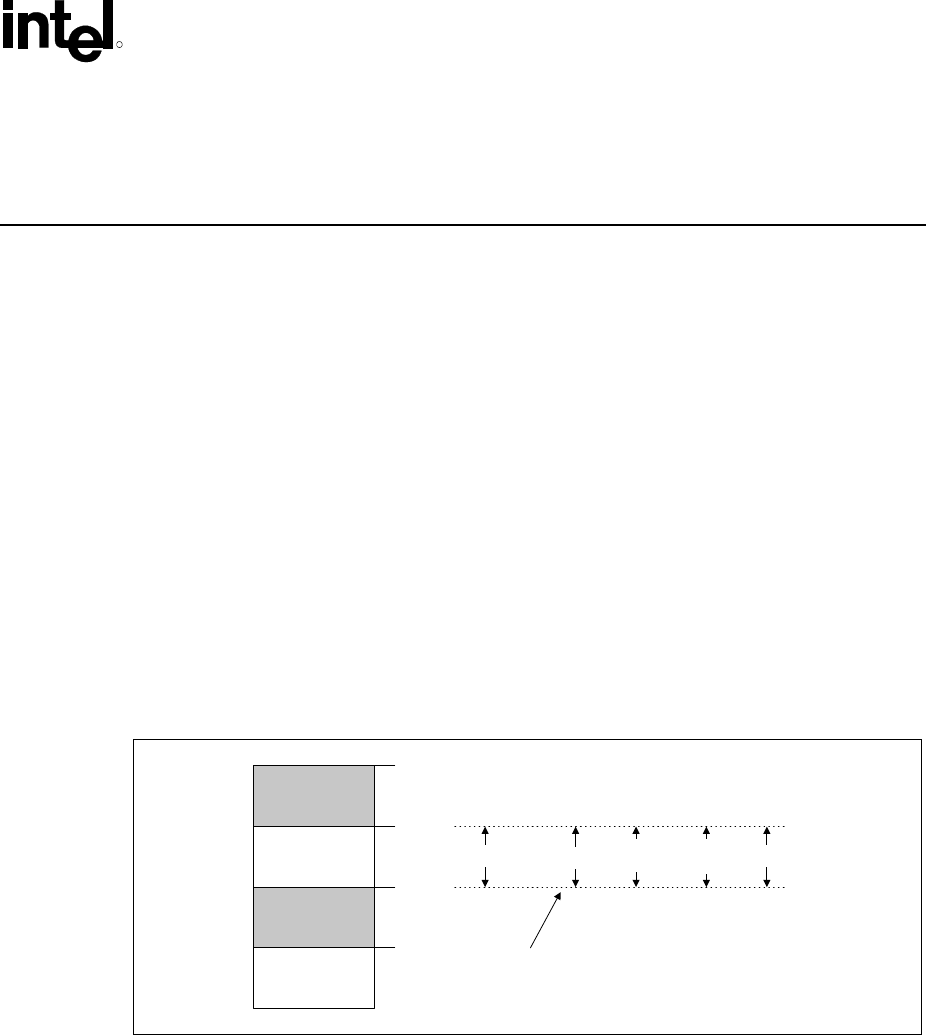

Figure 3. Addressable Memory Space

DOS Legacy Address

Range

System Memory

Address Range

PCI Memory Address

Range

Top of Low

Memory

1 MB

4 GB

Hub Interface

AGP

Graphics

Aperture

I/O

Aperture

APICs

Independently Programmable

Non-overlapping Windows

sys_addr_map_1

Additional System

Memory Address

Range

16 GB

These address ranges are always mapped to system memory, regardless of the system

configuration. Memory may be taken out of the system memory segment for use by System

Management Mode (SMM) hardware and software. The Top of Low Memory (TOM) register

defines the top of system memory.

Note that the address of the highest 16 MB quantity of valid memory in the system is placed into

the GBA15 register. For memory populations <3 GB, this value will be the same as the one

programmed into the TOM register. For other memory configurations, the two are unlikely to be

the same, since the PCI configuration portion of the BIOS software will program the TOM register

to the maximum value that is less than the amount of memory in the system and that allows enough

room for all populated PCI devices.