Register Description

R

Intel

®

82845 MCH for SDR Datasheet 75

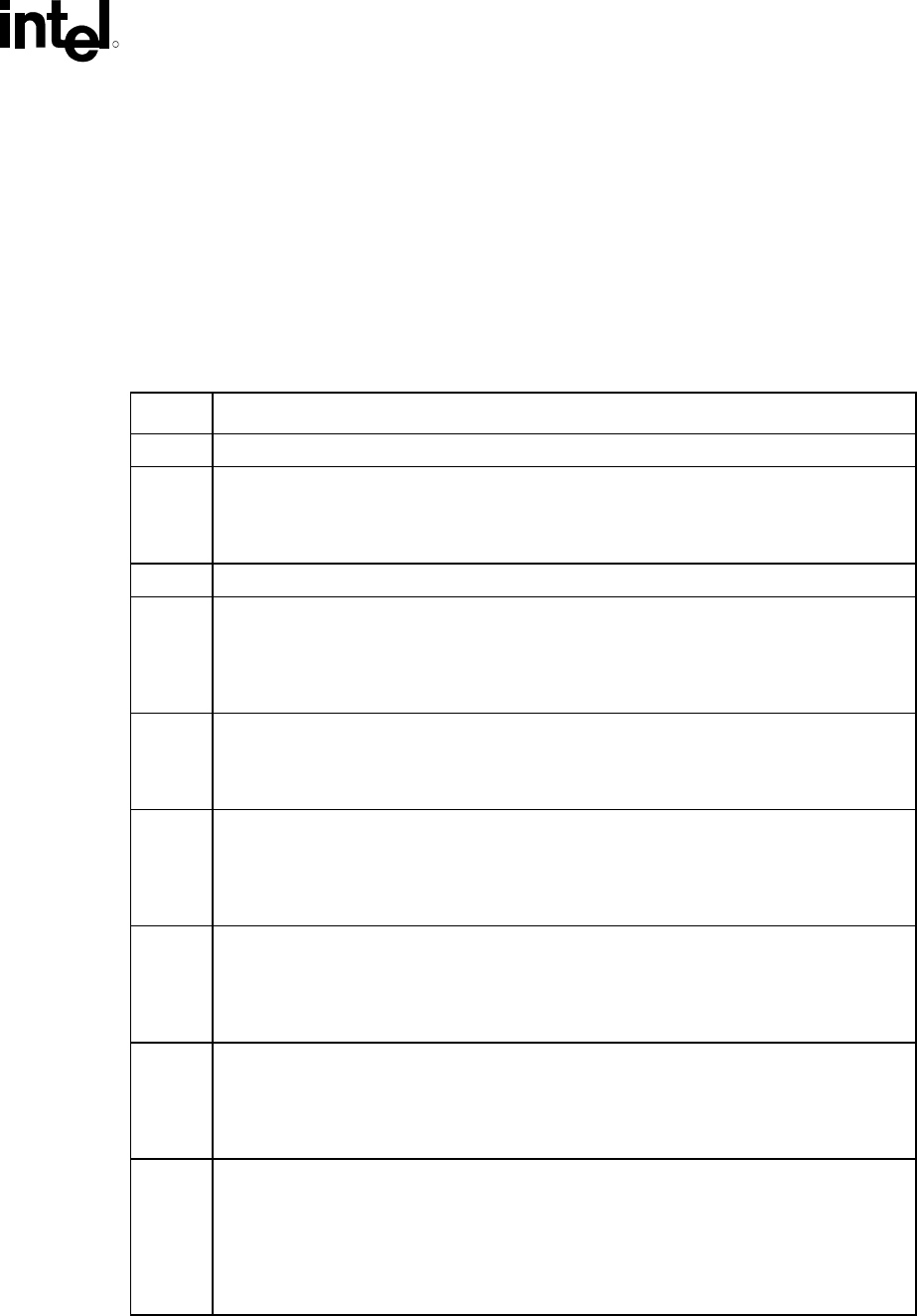

3.5.35 ERRSTS—Error Status Register (Device 0)

Address Offset: C8–C9h

Default Value: 0000h

Access: R/WC

Size: 16 bits

This register is used to report various error conditions via the hub interface messages to ICH2. An

SERR, SMI, or SCI error message may be generated via the hub interface on a zero to one

transition of any of these flags when enabled in the PCICMD/ERRCMD, SMICMD, or SCICMD

registers, respectively. These bits are set, regardless of whether or not the SERR is enabled and

generated.

Bit Description

15:10 Reserved.

9 LOCK to non-DRAM Memory Flag (LCKF).

0 = Software must write a 1 to clear this status bit.

1 = Indicates that a host initiated LOCK cycle targeting non-DRAM memory space occurred.

8:7 Reserved.

6 SERR on Hub Interface Target Abort (TAHLA).

0 = Software must write a 1 to clear this status bit.

1 = MCH detected that a MCH-originated hub interface cycle was terminated with a Target Abort

completion packet or special cycle.

5 MCH Detects Unimplemented Hub Interface Special Cycle (HIAUSC).

0 = Software must write a 1 to clear this status bit.

1 = MCH detected an Unimplemented Special Cycle on the hub interface.

4 AGP Access Outside of Graphics Aperture Flag (OOGF).

0 = Software must write a 1 to clear this status bit.

1 = Indicates that an AGP access occurred to an address that is outside of the graphics aperture

range.

3 Invalid AGP Access Flag (IAAF).

0 = Software must write a 1 to clear this status bit.

1 = Indicates that an AGP access was attempted outside of the graphics aperture and either to

the 640 KB – 1 MB range or above the top of memory.

2 Invalid Graphics Aperture Translation Table Entry (ITTEF).

0 = Software must write a 1 to clear this status bit.

1 = Indicates that an invalid translation table entry was returned in response to an AGP access

to the graphics aperture.

1 Multiple-bit DRAM ECC Error Flag (DMERR).

0 = After software completes the error processing, a value of 1 is written to this bit field to set the

value back to 0 and unlock the error logging mechanism.

1 = A memory read data transfer had an uncorrectable multiple-bit error. When this bit is set, the

address and device number that caused the error are logged in the EAP Register. Software

uses bits [1:0] to detect whether the logged error address is for Single or Multiple-bit error.