Register Description

R

64 Intel

®

82845 MCH for SDR Datasheet

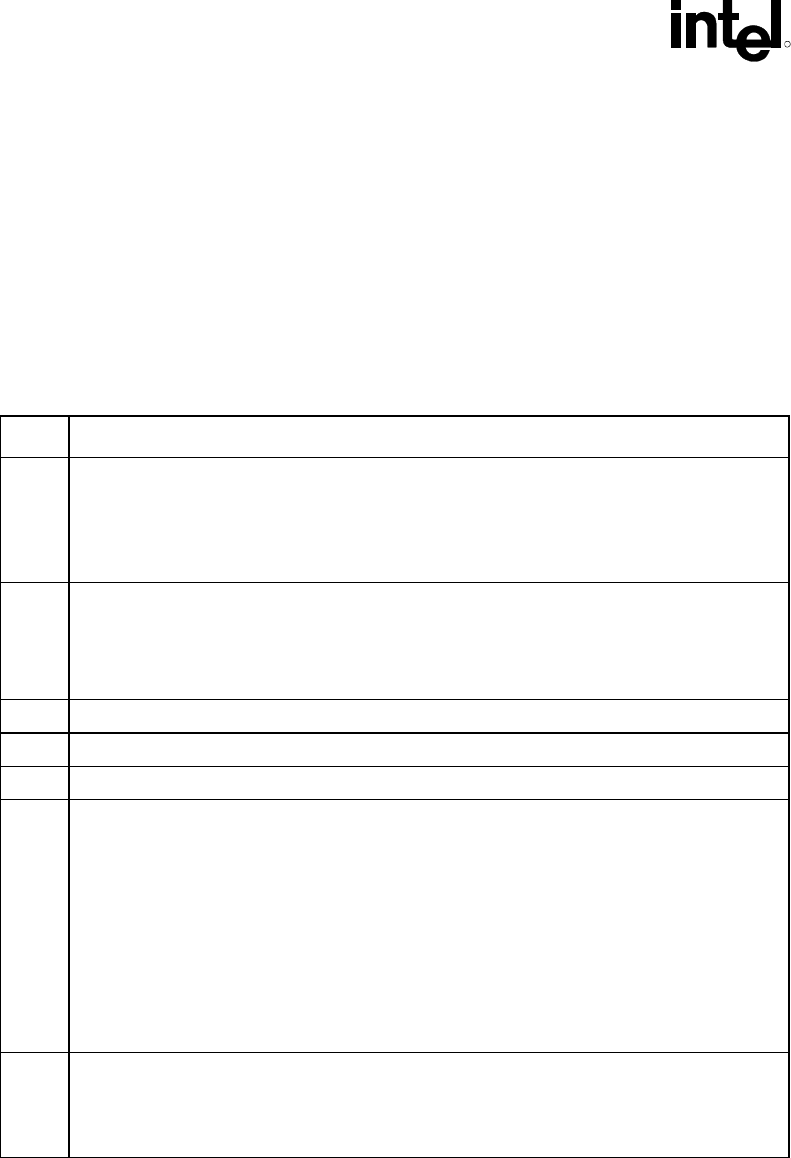

3.5.24 ESMRAMC—Extended System Mgmt RAM Control Register

(Device 0)

Address Offset: 9Eh

Default Value: 38h

Access: RO, R/W, R/WC, R/W/L

Size: 8 bits

The Extended SMRAM register controls the configuration of Extended SMRAM space. The

Extended SMRAM (E_SMRAM) memory provides a write-back cacheable SMRAM memory

space that is above 1 MB.

Bit Description

7 H_SMRAM_EN (H_SMRAME)—R/W/L. Controls the SMM memory space location (i.e., above 1

MB or below 1 MB). When G_SMRAME is 1 and H_SMRAME this bit is set to 1, the high

SMRAM memory space is enabled. SMRAM accesses from FEDA_0000h to FEDB_FFFFh are

remapped to DRAM address 000A0000h to 000BFFFFh.

Once D_LCK is set, this bit becomes read only.

6 E_SMRAM_ERR (E_SMERR)—R/WC.

0 = The software must write a 1 to this bit to clear it.

1 = This bit is set when host accesses the defined memory ranges in Extended SMRAM (High

Memory and T-segment) while not in SMM space and with the D-OPEN bit = 0.

5 SMRAM_Cache (SM_CACHE)—RO. Hardwired to 1.

4 SMRAM_L1_EN (SM_L1)—RO. Hardwired to 1.

3 SMRAM_L2_EN (SM_L2)—RO. Hardwired to 1.

2:1 TSEG_SZ[1-0] (T_SZ)—R/W. Selects the size of the TSEG memory block if enabled. This

memory is taken from the top of system memory space (i.e., TOM – TSEG_SZ), which is no

longer claimed by the memory controller (all accesses to this space are sent to the hub interface

if TSEG_EN is set). This field decodes as follows:

00 = (TOM–128 KB) to TOM

01 = (TOM–256 KB) to TOM

10 = (TOM–512 KB) to TOM

11 = (TOM–1 MB) to TOM

Once D_LCK is set, this bit becomes read only.

0 TSEG_EN (T_EN)—R/W/L. Enabling of SMRAM memory (TSEG, 128 KB, 256 KB, 512 KB or

1 MB of additional SMRAM memory) for Extended SMRAM space only. When G_SMRAME =1

and TSEG_EN = 1, the TSEG is enabled to appear in the appropriate physical address space.

Once D_LCK is set, this bit becomes read only.