Signal Description

R

28 Intel

®

82845 MCH for SDR Datasheet

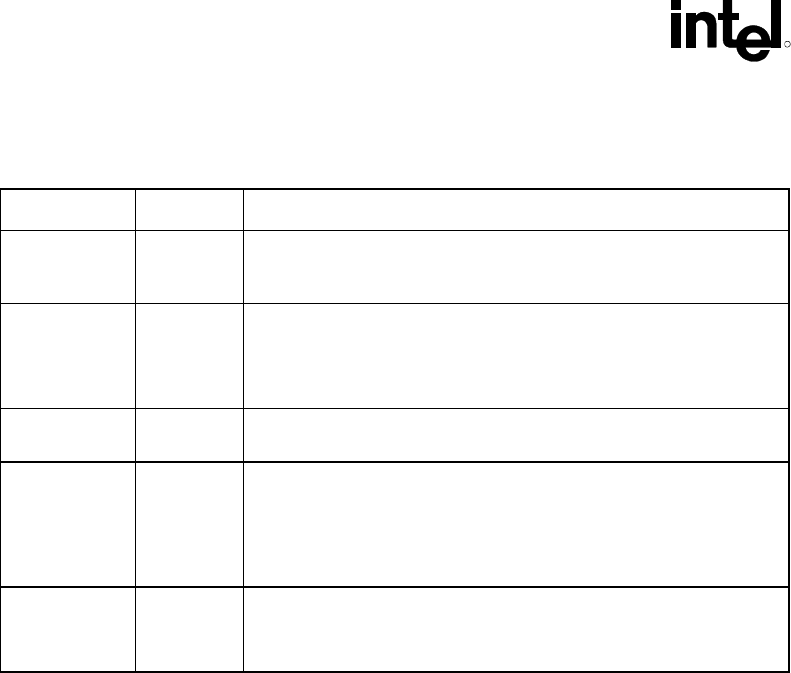

2.5 Clocks, Reset, and Miscellaneous Signals

Signal Name Type Description

BCLK

BCLK#

I

CMOS

Differential Host Clock In: These pins receive a differential host clock

from the external clock synthesizer. This clock is used by all of the MCH

logic that is in the host clock domain.

66IN I

CMOS

66 MHz Clock In: This pin receives a 66 MHz clock from the clock

synthesizer. This clock is used by AGP/PCI and hub interface clock

domains.

Note: That this clock input is 3.3 V tolerant.

SCK[11:0] O

CMOS

System Memory Clocks (SDR): These signals deliver a synchronized

clock to the DIMMs. There are two per row.

RSTIN# I

CMOS

Reset In: When asserted, this signal asynchronously resets the MCH

logic. RSTIN# is connected to the PCIRST# output of the ICH2. All

AGP/PCI output and bi-directional signals will also three-state compliant

to PCI Rev 2.0 and 2.1 specifications.

Note: This input needs to be 3.3 V tolerant.

TESTIN# I

CMOS

Test Input: This pin is used for manufacturing and board level test

purposes.

Note: This signal has an internal pull-up resistor.