Register Description

R

50 Intel

®

82845 MCH for SDR Datasheet

3.5.10 APBASE—Aperture Base Configuration Register (Device 0)

Offset: 10–13h

Default: 0000_0008h

Access: R/W, RO

Size: 32 bits

The APBASE is a standard PCI Base Address register that is used to set the base of the Graphics

Aperture. The standard PCI Configuration mechanism defines the base address configuration

register such that only a fixed amount of space can be requested (dependent on which bits are

hardwired to 0 or behave as hardwired to 0). To allow for flexibility (of the aperture), an

additional register called APSIZE is used as a “back-end” register to control, which bits of the

APBASE will behave as hardwired to 0. This register will be programmed by the MCH specific

BIOS code that runs before any of the generic configuration software is run.

Note: Bit 9 of the MCHCFG register is used to prevent accesses to the aperture range before this

register

is initialized by the configuration software and the appropriate translation table structure has been

established in the system memory.

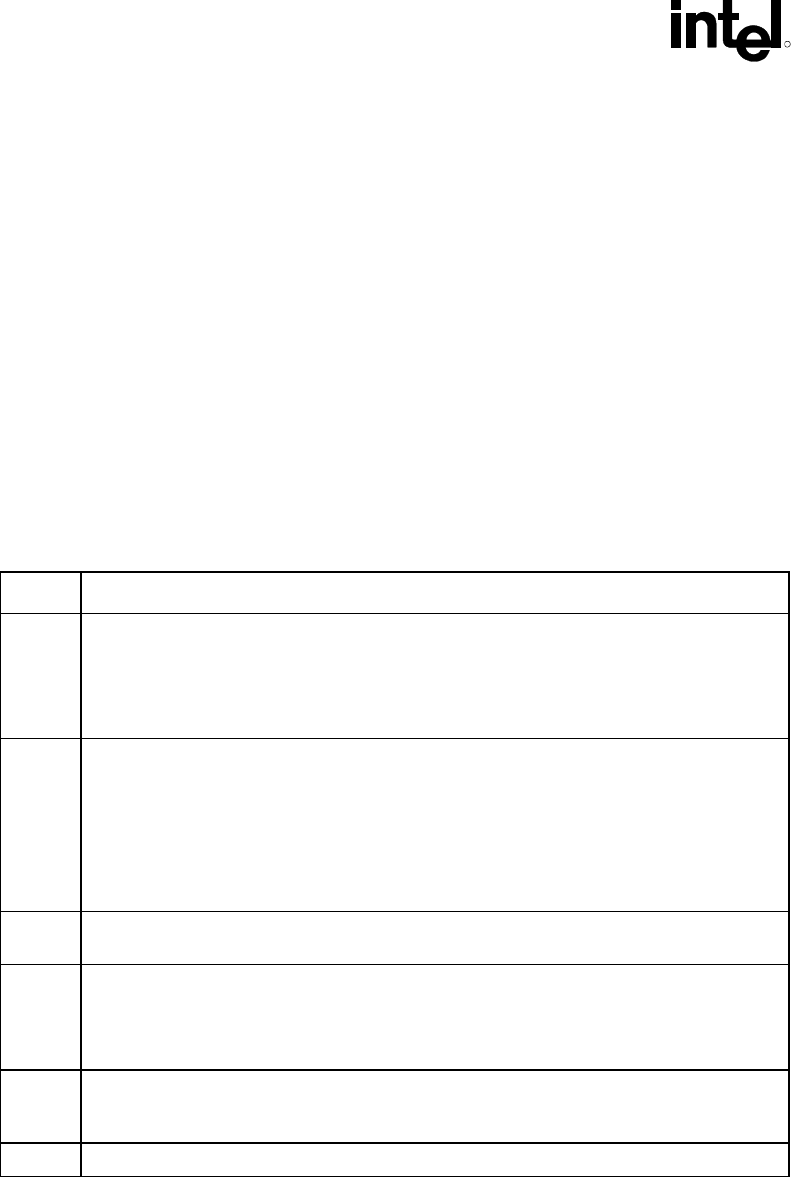

Bit Description

31:28 Upper Programmable Base Address—R/W. These bits are part of the aperture base set by

configuration software to locate the base address of the graphics aperture. They correspond to

bits [31:28] of the base address in the processor's address space that will cause a graphics

aperture translation to be inserted into the path of any memory read or write.

Default = 0000

27:22 Middle “Hardwired”/Programmable Base Address—R/W. These bits are part of the aperture

base set by configuration software to locate the base address of the graphics aperture. They

correspond to bits [27:4] of the base address in the processor's address space that will cause a

graphics aperture translation to be inserted into the path of any memory read or write. These

bits can behave as though they were hardwired to 0, if programmed to do so by the APSIZE bits

of the APSIZE register. This causes configuration software to understand that the granularity of

the graphics aperture base address is either finer or more coarse, depending on the bits set by

MCH-specific configuration software in APSIZE.

21:4 Lower “Hardwired” Base Address—RO. Hardwired to 0s. This forces a minimum aperture

size selected by this register to be 4 MB.

3 Prefetchable—RO. This bit is hardwired to 1 to identify the Graphics Aperture range as

prefetchable as per the PCI Local Bus Specification for the base address registers.

There are no side effects on reads, the device returns all bytes on reads, regardless of the byte

enables, and the MCH may merge processor writes into this range without causing errors.

2:1 Type—RO. These bits determine addressing type and they are hardwired to “00” to indicate that

address range defined by the upper bits of this register can be located anywhere in the 32-bit

address space.

0 Memory Space Indicator—RO. Hardwired to 0 to identify aperture range as a memory range.