Signal Description

R

24 Intel

®

82845 MCH for SDR Datasheet

2.4 AGP Interface Signals

2.4.1 AGP Addressing Signals

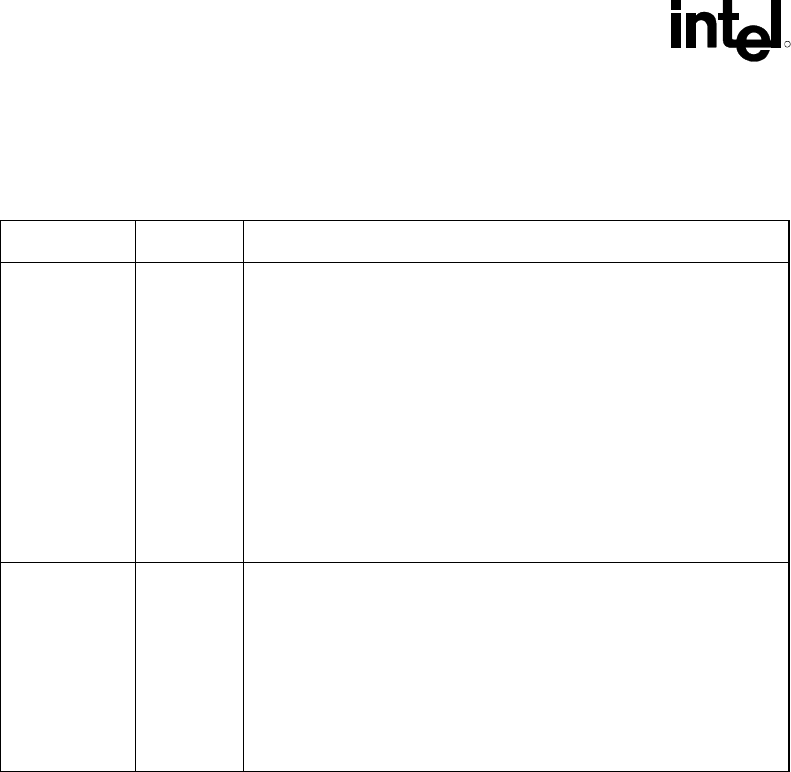

Signal Name Type Description

PIPE# I

AGP

Pipelined Read: This signal is asserted by the AGP master to indicate a

full-width address is to be enqueued on by the target using the AD bus.

One address is placed in the AGP request queue on each rising clock

edge while PIPE# is asserted. When PIPE# is deasserted, no new

requests are queued across the AD bus.

During SBA Operation: Not Used.

During FRAME# Operation: Not Used.

PIPE# is a sustained three-state signal from masters (graphics

controller), and is an MCH input.

Note: Initial AGP designs may not use PIPE# (i.e., PCI only 66 MHz).

Therefore, an 8 kΩ pull-up resistor connected to this pin is

required on the motherboard.

SBA[7:0] I

AGP

Sideband Address: These signals are used by the AGP master

(graphics controller) to place addresses into the AGP request queue.

The SBA bus and AD bus operate independently. That is, a transaction

can proceed on the SBA bus and the AD bus simultaneously.

During PIPE# Operation: Not Used.

During FRAME# Operation: Not Used.

Note: When sideband addressing is disabled, these signals are

isolated (no external/internal pull-up resistors are required).

NOTE: The above table contains two mechanisms to queue requests by the AGP master. Note that the

master can only use one mechanism. The master may not switch methods without a full reset of the

system. When PIPE# is used to queue addresses the master is not allowed to queue addresses using

the SBA bus. For example, during configuration time, if the master indicates that it can use either

mechanism, the configuration software will indicate which mechanism the master will use. Once this

choice has been made, the master will continue to use the mechanism selected until the master is

reset (and reprogrammed) to use the other mode. This change of modes is not a dynamic mechanism

but rather a static decision when the device is first being configured after reset.