Register Description

R

38 Intel

®

82845 MCH for SDR Datasheet

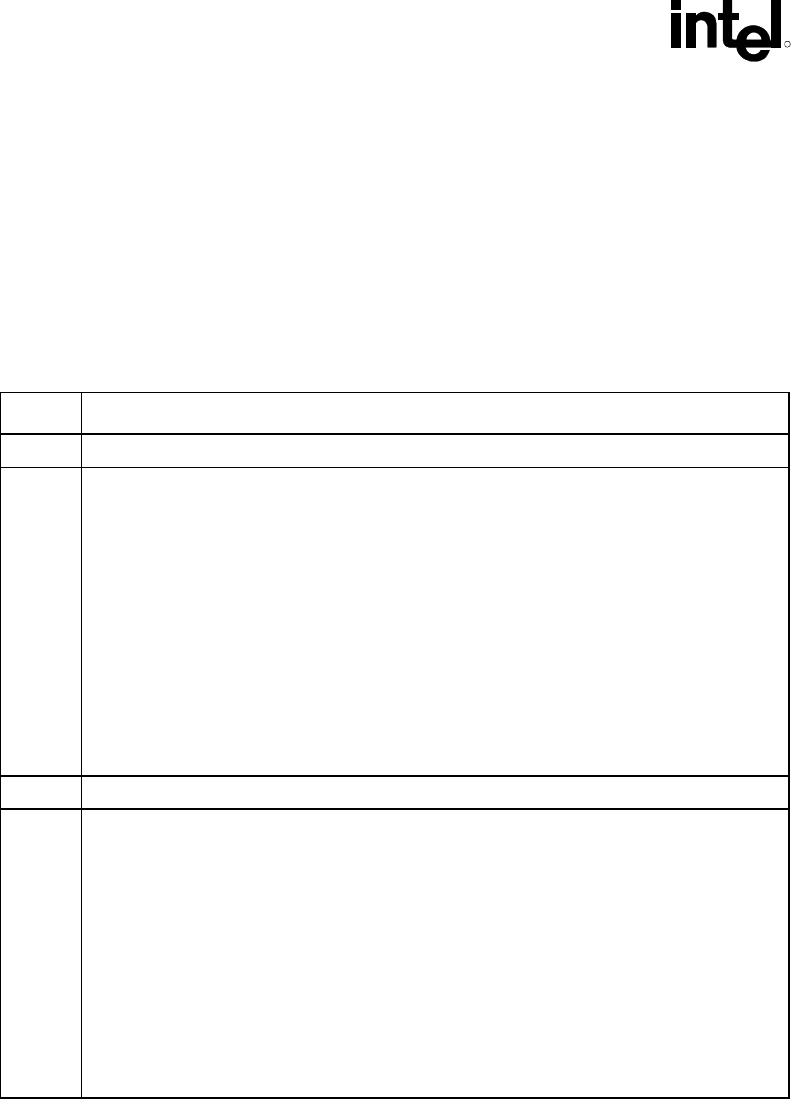

3.4.2 DQCMDSTR—Strength Control Register (SDQ and CMD

Signal Groups)

Memory Address Offset: 30h

Default Value: 00h

Access: R/W

Size: 8 bits

This register controls the drive strength of the I/O buffers for the DQ/DQS and CMD signal

groups.

Bit Descriptions

7 Reserved.

6:4 CMD Strength Control (SRAS#, SCAS#, SWE#, SMA[12:0], SBS[1:0]). This field selects the

signal drive strength.

000 = 0.75 X (default)

001 = 1.00 X

010 = 1.25 X

011 = 1.50 X

100 = 2.00 X

101 = 2.50 X

110 = 3.00 X

111 = 4.00 X

3 Reserved.

2:0 SDQ/SDQS Strength Control. This field selects the signal drive strength.

000 = 0.75 X (default)

001 = 1.00 X

010 = 1.25 X

011 = 1.50 X

100 = 2.00 X

101 = 2.50 X

110 = 3.00 X

111 = 4.00 X