Power Management

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

8-8 Freescale Semiconductor

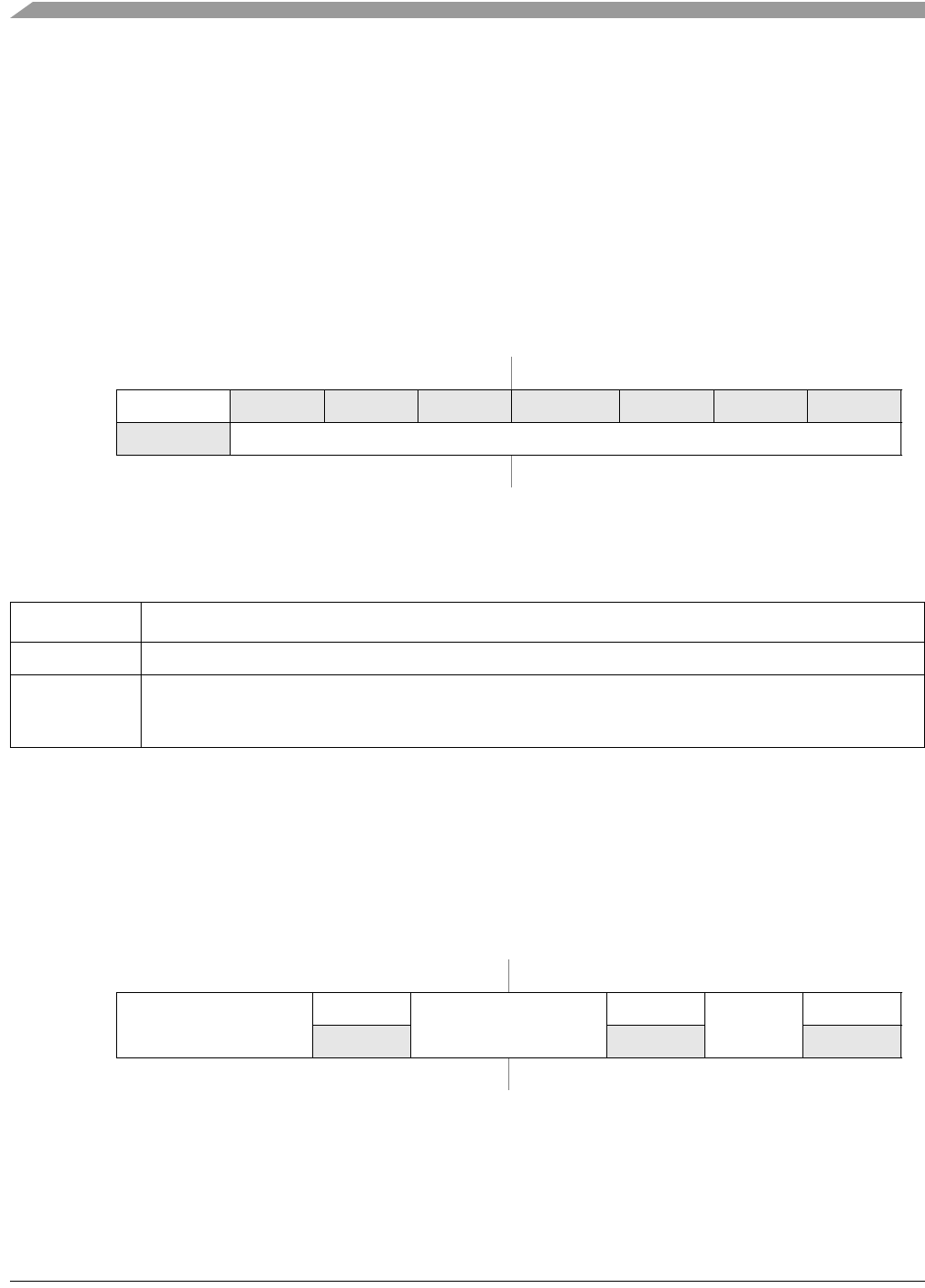

8.2.4 Peripheral Power Management Clear Register (PPMRC)

The PPMRC register provides a simple memory-mapped mechanism to clear a given bit in the PPMRx

registers to enable the clock for a given IPS module without the need to perform a read-modify-write on

the PPMRx. The data value on a register write causes the corresponding bit in the PPMRx register to be

cleared. A data value of 64 to 127 provides a global clear function, forcing the entire contents of the

PPMRx to be zeroed, enabling all IPS module clocks. In the event on simultaneous writes of the PPMRS

and PPMRC, the write to the PPMRC takes priority. Reads of this register return all zeroes. See Figure 8-5

and Table 8-7 for the PPMRC definition.

8.2.5 Low-Power Control Register (LPCR)

The LPCR controls chip operation and module operation during low-power modes. It specifies the

low-power mode entered when the STOP instruction is issued, and controls clock activity in this

low-power mode.

IPSBAR

Offset: 0x0022 (PPMRC)

Access: write-only

7 6543210

R 0

W PPMRC

Reset: 0 0 0 0 0 0 0 0

Figure 8-5. Peripheral Power Management Clear Register (PPMRC)

Table 8-7. PPMRC Field Descriptions

Field Description

7 Reserved, should be cleared.

6–0

PPMRC

Clear Module Clock Disable

0–63 Clear corresponding bit in PPMRx, enabling the module clock

64–127 Clear all bits in PPMRx, enabling all the module clocks

IPSBAR

Offset: 0x11_0007 (LPCR)

Access: read/write

76543210

R

LPMD

0

STPMD

0

LVDSE

0

W

Reset:00000010

Figure 8-6. Low-Power Control Register (LPCR)