Multiply-Accumulate Unit (MAC)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 4-9

4.3.3 MAC Instruction Execution Times

The instruction execution times for the MAC can be found in Section 3.3.5.6, “MAC Instruction Execution

Times”.

4.3.4 Data Representation

MACSR[S/U,F/I] selects one of the following three modes, where each mode defines a unique operand

type:

1. Two’s complement signed integer: In this format, an N-bit operand value lies in the range -2

(N-1)

< operand < 2

(N-1)

- 1. The binary point is right of the lsb.

2. Unsigned integer: In this format, an N-bit operand value lies in the range 0 < operand < 2

N

- 1. The

binary point is right of the lsb.

3. Two’s complement, signed fractional: In an N-bit number, the first bit is the sign bit. The remaining

bits signify the first N-1 bits after the binary point. Given an N-bit number, a

N-1

a

N-2

a

N-3

... a

2

a

1

a

0

,

its value is given by the equation in Equation 4-3.

Eqn. 4-3

This format can represent numbers in the range -1 < operand < 1-2

(N-1)

.

For words and longwords, the largest negative number that can be represented is -1, whose internal

representation is 0x8000 and 0x8000_0000, respectively. The largest positive word is 0x7FFF or (1 - 2

-15

);

the most positive longword is 0x7FFF_FFFF or (1 - 2

-31

).

4.3.5 MAC Opcodes

MAC opcodes are described in the ColdFire Programmer’s Reference Manual.

Remember the following:

• Unless otherwise noted, the value of MACSR[N,Z] is based on the result of the final operation that

involves the product and the accumulator.

• The overflow (V) flag is managed differently. It is set if the complete product cannot be represented

as a 32-bit value (this applies to 32 × 32 integer operations only) or if the combination of the

product with the accumulator cannot be represented in the given number of bits. This indicator is

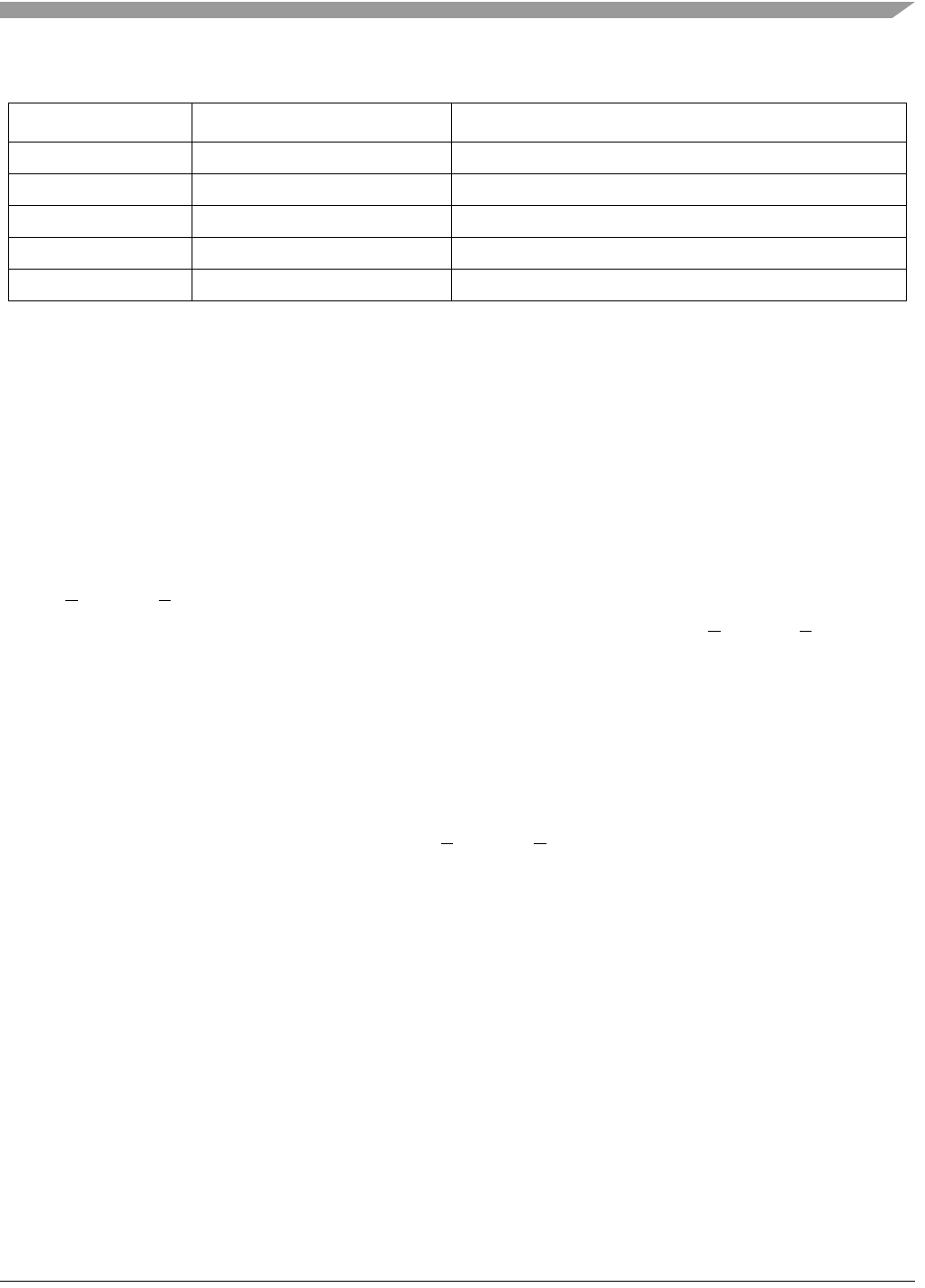

Load MACSR move.l {Ry,#imm},MACSR Writes a value to MACSR

Store MACSR move.l MACSR,Rx Write the contents of MACSR to a CPU register

Store MACSR to CCR move.l MACSR,CCR Write the contents of MACSR to the CCR

Load MAC Mask Reg move.l {Ry,#imm},MASK Writes a value to the MASK register

Store MAC Mask Reg move.l MASK,Rx Writes the contents of the MASK to a CPU register

Table 4-6. MAC Instruction Summary (continued)

Command Mnemonic Description

value 1 a

N1–

⋅()–2

i1N–+()–

ai⋅

i0=

N2–

∑

+=