System Control Module (SCM)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 12-9

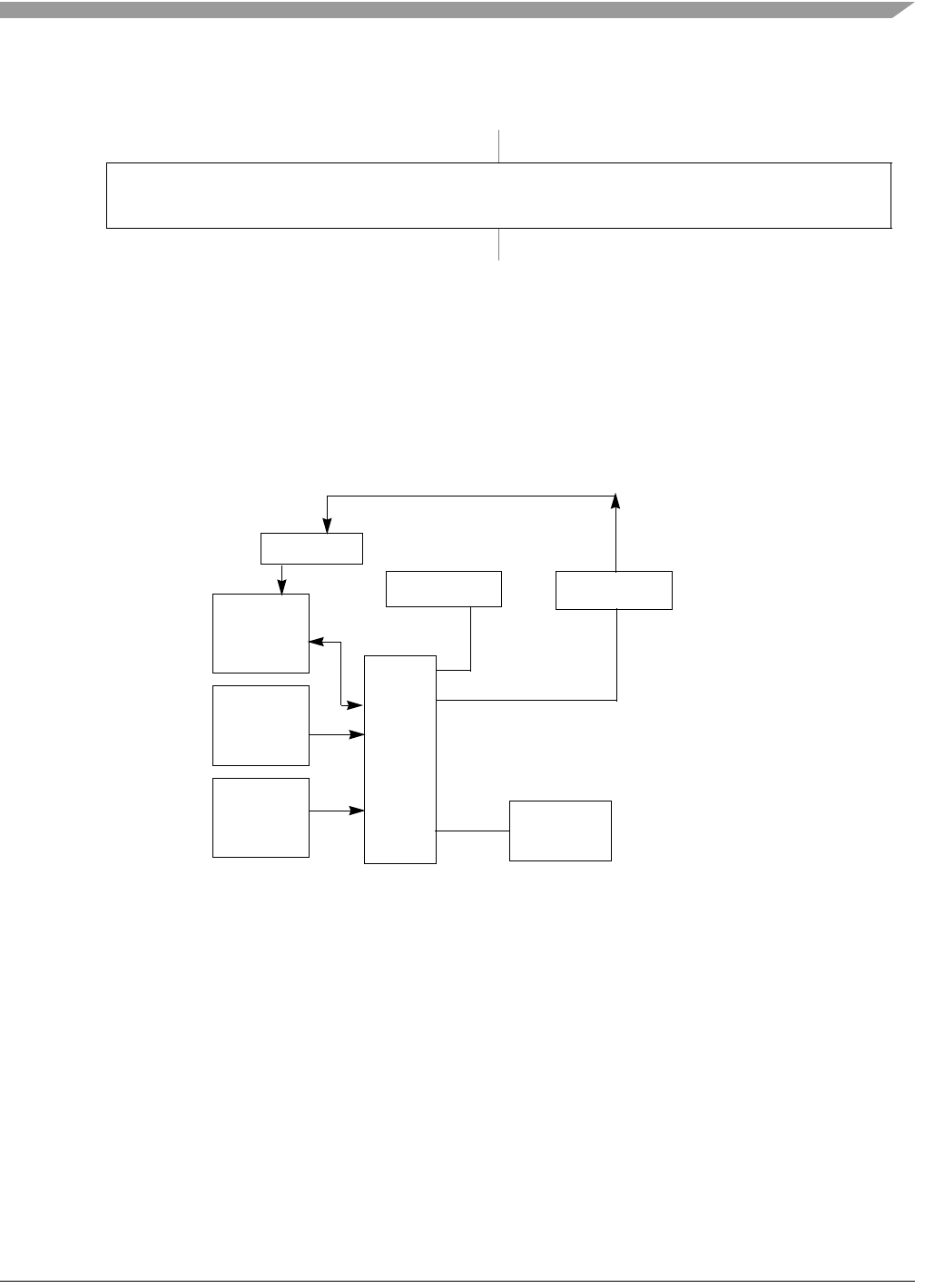

12.6 Internal Bus Arbitration

The internal bus arbitration is performed by the on-chip bus arbiter, which containing the arbitration logic

that controls which of up to four MBus masters (M0–M3 in Figure 12-6) has access to the external buses.

The function of the arbitration logic is described in this section.

Figure 12-6. Arbiter Module Functions

12.6.1 Overview

The basic functionality is that of a 2-port, pipelined internal bus arbitration module with the following

attributes:

• The master pointed to by the current arbitration pointer may get on the bus with zero latency if the

address phase is available. All other requesters face at least a one cycle arbitration pipeline delay

to meet bus timing constraints on address phase hold.

• If a requester receives an immediate address phase (that is, it is pointed to by the current arbitration

pointer and the bus address phase is available), it is the current bus master and is ignored by

arbitration. All remaining requesting ports are evaluated by the arbitration algorithm to determine

the next-state arbitration pointer.

IPSBAR

Offset:

0x0013 (CWSR) Access: read/write

76543210

R

CWSR[7:0]

W

Reset: Uninitialized

Figure 12-5. Core Watchdog Service Register (CWSR)

SRAM1

MPARK

RAMBAR

CPU

M0

DMA

M2

Internal

M1

Bus

Master

Internal

MARB

Modules

Back door to SRAM and flash