Analog-to-Digital Converter (ADC)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

26-10 Freescale Semiconductor

26.4.5 Sample Disable Register (ADSDIS)

This register is an extension to the ADLST1and ADLST2, providing the ability to enable only the desired

samples programmed in the SAMPLE0–SAMPLE7. At reset, all samples are enabled. For example, if in

sequential mode and bit DS5 is set to 1, SAMPLE0 through SAMPLE4 are sampled. However, if in

parallel mode and bits DS5 or DS1 are set to 1, only SAMPLE0 and SAMPLE4 are sampled.

Table 26-8. ADLST2 Field Descriptions

Field Description

15 Reserved, should be cleared.

14–12

SAMPLE7

Sample input channel select 7. The settings for this field are given in Tabl e 26-9 .

11 Reserved, should be cleared.

10–8

SAMPLE6

Sample input channel select 6. The settings for this field are given in Tabl e 26-9 .

7 Reserved, should be cleared.

6–4

SAMPLE5

Sample input channel select 5. The settings for this field are given in Tabl e 26-9 .

3 Reserved, should be cleared.

2–0

SAMPLE4

Sample input channel select 4. The settings for this field are given in Tabl e 26-9 .

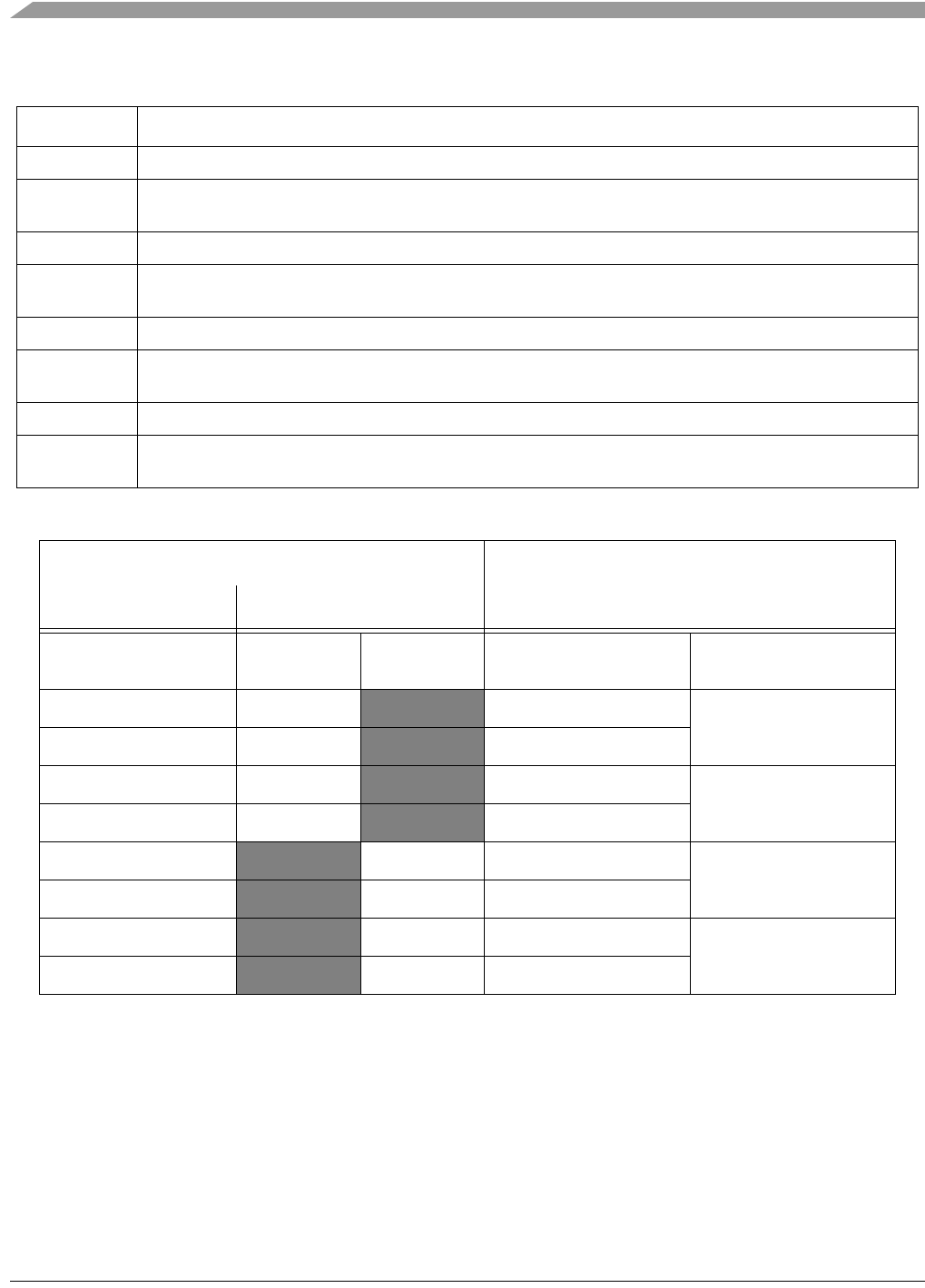

Table 26-9. ADC Input Conversion for Sample Bits

SAMPLEn[2:0]

ADC Input Pins Selected

Sequential Mode Parallel Mode

n=0,1,2,...,7 n=0,1,2,3

(Conv. A)

n=4,5,6,7

(Conv. B)

Single Ended Differential

000 000

AN0 AN0+, AN1–

001 001

AN1

010 010

AN2 AN2+, AN3–

011 011

AN3

100

100 AN4 AN4+, AN5–

101

101 AN5

110

110 AN6 AN6+, AN7–

111

111 AN7