Edge Port Module (EPORT)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 16-3

16.4.1 EPORT Pin Assignment Register (EPPAR)

The EPORT pin assignment register (EPPAR) controls the function of each pin individually.

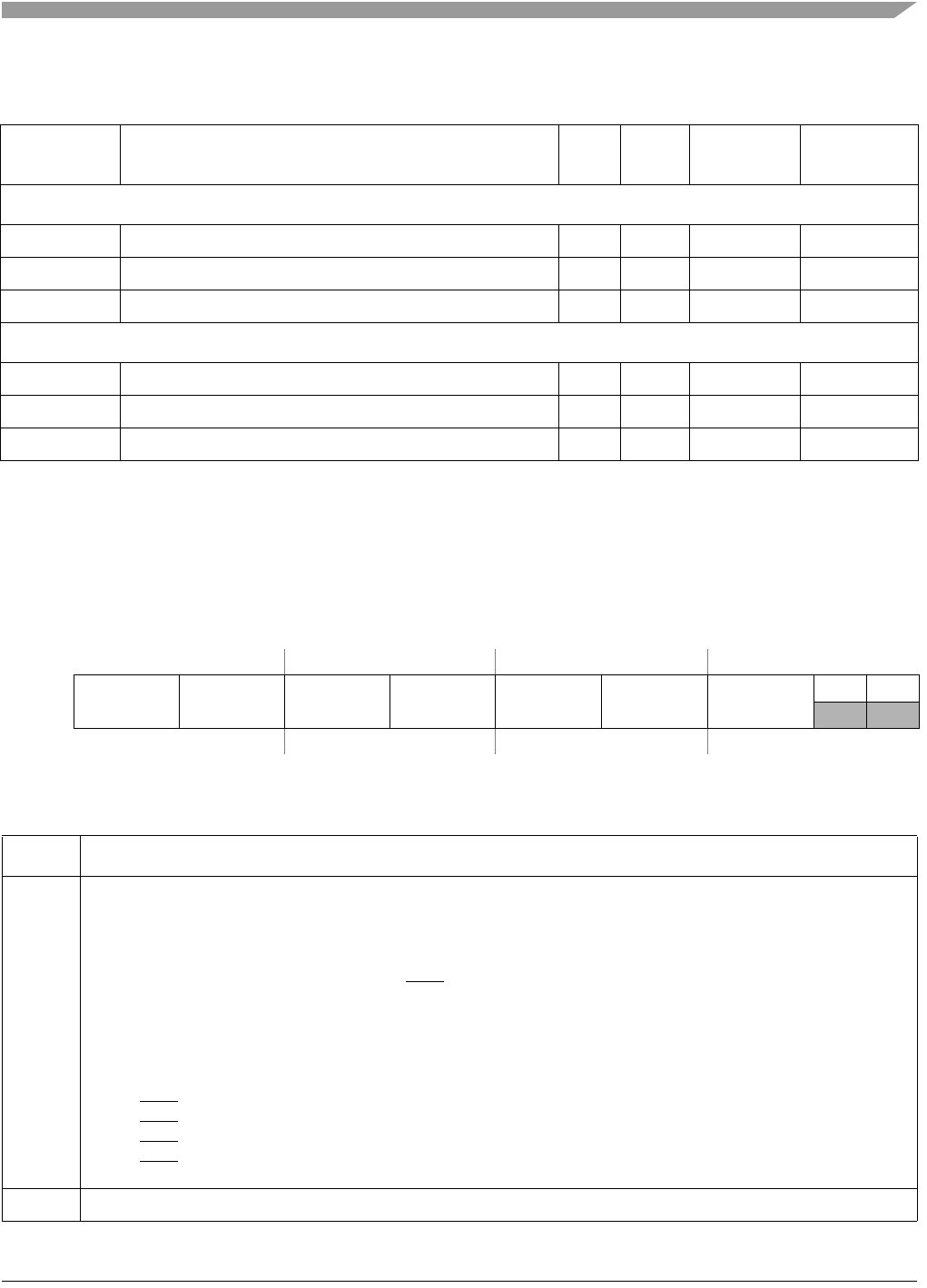

Table 16-2. Edge Port Module Memory Map

IPSBAR

Offset

Register

Width

(bits)

Access Reset Value Section/Page

Supervisor Access Only Registers

1

1

User access to supervisor-only address locations have no effect and result in a bus error.

0x13_0000 EPORT Pin Assignment Register (EPPAR) 16 R/W 0x0000 16.4.1/16-3

0x13_0002 EPORT Data Direction Register (EPDDR) 8 R/W 0x00 16.4.2/16-4

0x13_0003 EPORT Interrupt Enable Register (EPIER) 8 R/W 0x00 16.4.3/16-4

Supervisor/User Access Registers

0x13_0004 EPORT Data Register (EPDR) 8 R/W 0xFF 16.4.4/16-5

0x13_0005 EPORT Pin Data Register (EPPDR) 8 R See Section 16.4.5/16-5

0x13_0006 EPORT Flag Register (EPFR) 8 R/W 0x00 16.4.6/16-6

IPSBAR

Offset:

0x13_0000 (EPPAR) Access: Supervisor read/write

1514131211109876543210

R

EPPA7 EPPA6 EPPA5 EPPA4 EPPA3 EPPA2 EPPA1

W

Reset0000000000000000

Figure 16-2. EPORT Pin Assignment Register (EPPAR)

Table 16-3. EPPAR Field Descriptions

Field Description

15–2

EPPAn

EPORT Pin Assignment Select Fields. The read/write EPPAn fields configure EPORT pins for level detection and

rising and/or falling edge detection.

Pins configured as level-sensitive are active-low (logic 0 on the external pin represents a valid interrupt request).

Level-sensitive interrupt inputs are not latched. To guarantee that a level-sensitive interrupt request is acknowledged,

the interrupt source must keep the signal asserted until acknowledged by software. Level sensitivity must be selected

to bring the device out of stop mode with an IRQ

n interrupt.

Pins configured as edge-triggered are latched and need not remain asserted for interrupt generation. A pin

configured for edge detection can trigger an interrupt regardless of its configuration as input or output.

Interrupt requests generated in the EPORT module can be masked by the interrupt controller module. EPPAR

functionality is independent of the selected pin direction.

Reset clears the EPPAn fields.

00 Pin IRQ

n level-sensitive

01 Pin IRQ

n rising edge triggered

10 Pin IRQ

n falling edge triggered

11 Pin IRQ

n falling edge and rising edge triggered

1–0 Reserved, must be cleared.