MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 29-1

Chapter 29

IEEE 1149.1 Test Access Port (JTAG)

29.1 Introduction

The Joint Test Action Group (JTAG) is a dedicated user-accessible test logic compliant with the

IEEE 1149.1 standard for boundary-scan testability, which helps with system diagnostic and

manufacturing testing.

This architecture provides access to all data and chip control pins from the board-edge connector through

the standard four-pin test access port (TAP) and the JTAG reset pin, TRST.

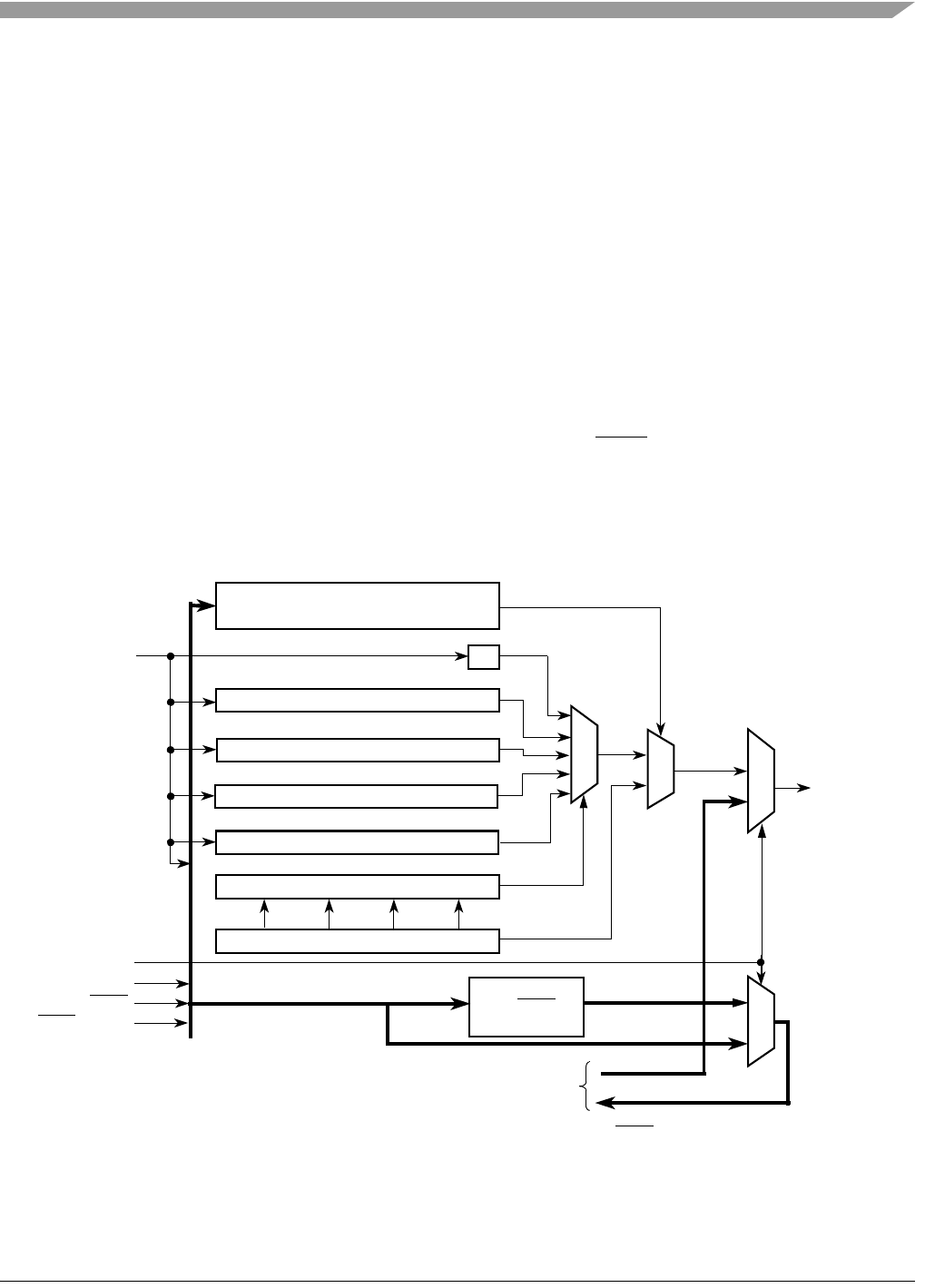

29.1.1 Block Diagram

Figure 29-1 shows the block diagram of the JTAG module.

Figure 29-1. JTAG Block Diagram

256-bit Boundary Scan Register

TDO/DSO

BKPT

4-bit TAP Instruction Register

30

1-bit Bypass Register

32-bit IDCODE Register

TRST/DSCLK

TCLK

TMS/BKPT

031

0

TAP Controller

TDI/DSI

1

0

JTAG Module

to Debug Module

4-bit TAP Instruction Decoder

1

0

Disable DSCLK

Force BKPT = 1

DSI = 0

JTAG_EN

DSO

DSI

DSCLK

255

7-bit JTAG_CFM_CLKDIV Register

06

3-bit TEST_CTRL Register

02