General Purpose I/O Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

13-10 Freescale Semiconductor

13.6.5 Pin Assignment Registers

All pin assignment registers are read/write. Refer to Table 2-1 for the different functions assignable to each

pin.

Some signals can be assigned to different pins (see Table 2-1). However, a signal should not be assigned

to more than one pin at the same time. If a signal is assigned to two or more pins simultaneously, the result

is undefined.

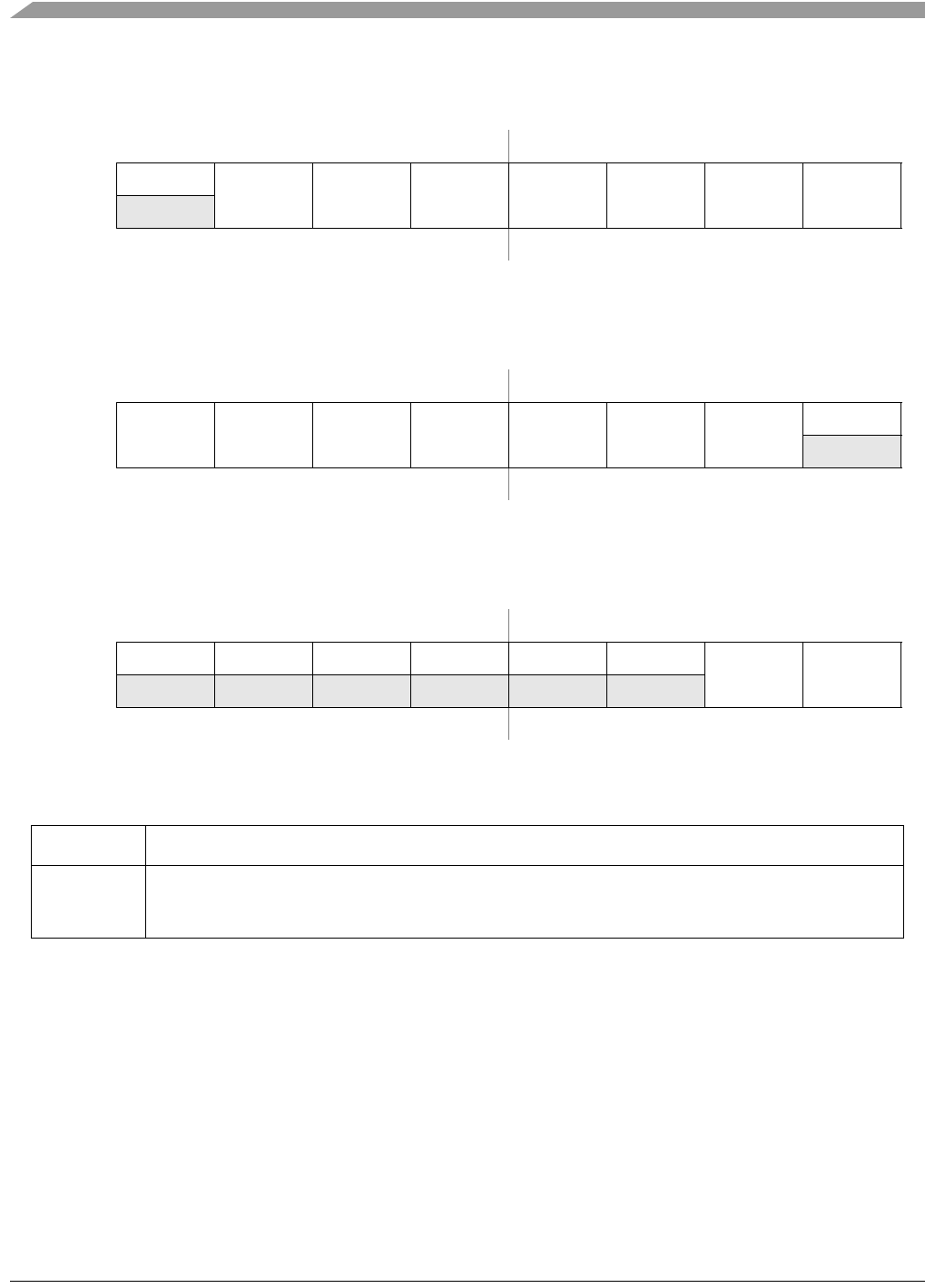

IPSBAR

Offset: 0x10_0054 (CLRQS)

Access: User read/write

76543210

R 0

CLRn6CLRn5CLRn4CLRn3CLRn2CLRn1CLRn0

W

Reset:00000000

Figure 13-19. Port QS Clear Output Data Register (CLRQS)

IPSBAR

Offset: 0x10_0050 (CLRNQ)

Access: User read/write

76543210

R

CLRn7CLRn6CLRn5CLRn4CLRn3CLRn2CLRn1

0

W

Reset:00000000

Figure 13-20. Port NQ Clear Output Data Register (CLRNQ)

IPSBAR

Offset: 0x10_0053 (CLRAS)

Access: User read/write

76543210

R 0 0 0 000

CLRn1CLRn0

W

Reset:00000000

Figure 13-21. Port AS Clear Output Data Register (CLRAS)

Table 13-5. CLRn Field Descriptions

Field Description

CLRnxPortnx pin data/set data bits.

1 Never returned for reads; no effect for writes

0 Always returned for reads; clears corresponding port nx bit for writes